Organizacija memorije MPS-a. segmentacija memorije. Izračun adrese. Interna cache memorija.

Memorija mikroprocesorskog sustava obavlja funkciju privremene ili trajne pohrane podataka i naredbi. Količina memorije određuje dopuštenu složenost algoritama koje izvršava sustav, kao i, u određenoj mjeri, brzinu sustava u cjelini. Memorijski moduli se izvode na memorijskim čipovima (operativnim ili trajnim). Flash memorija se sve više koristi kao dio mikroprocesorskih sustava (engleski - brza memorija), što je nepromjenjiva memorija s mogućnošću višekratnog prepisivanja sadržaja.

Za spajanje memorijskog modula na sistemsku sabirnicu koriste se blokovi sučelja koji uključuju dekoder adrese (selektor), krug za obradu upravljačkog signala sabirnice i međuspremnike podataka (slika 7.4.1).

Slika 7.4.1. Dijagram povezivanja memorijskog modula.

U memorijskom prostoru mikroprocesorskog sustava obično postoji nekoliko posebnih područja koja obavljaju posebne funkcije. To uključuje:

– programska memorija za pokretanje koja se izvršava na ROM-u ili flash memoriji;

- memorija za stog ili stog (Stack) - ovo je dio RAM memorija, dizajniran za privremenu pohranu podataka;

– tablicu vektora prekida koja sadrži adrese početka programa za rukovanje prekidima;

– memorija uređaja spojenih na sistemsku sabirnicu.

Svi ostali dijelovi memorijskog prostora u pravilu imaju univerzalna namjena. Mogu sadržavati i podatke i programe (naravno, u slučaju arhitekture s jednom sabirnicom).

Često se memorijski prostor dijeli na segmente s programski promjenjivom adresom početka segmenta i sa fiksna veličina segment. Na primjer, u procesoru Intel 8086 segmentacija memorije je organizirana na sljedeći način.

Cjelokupna memorija sustava nije predstavljena kao kontinuirani prostor, već kao nekoliko dijelova - segmenata date veličine(po 64 KB), čiji se položaj u memorijskom prostoru može programski promijeniti.

Za pohranjivanje memorijskih adresnih kodova ne koriste se zasebni registri, već parovi registara:

Segmentni registar određuje adresu početka segmenta (tj. poziciju segmenta u memoriji);

Registar pokazivača (offset register) određuje položaj radne adrese unutar segmenta.

U ovom slučaju, fizička 20-bitna memorijska adresa dodijeljena vanjskoj adresnoj sabirnici formira se kao što je prikazano na slici 7.4.2, odnosno zbrajanjem pomaka i adrese segmenta s pomakom od 4 bita.

Slika 7.4.2. Formiranje adrese fizičke memorije iz adrese segmenta i pomaka.

Položaj ove adrese u memoriji prikazan je na slici 7.4.3.

Slika 7.4.3. Mjesto fizičke adrese u memoriji

Segment može započeti samo na 16-bajtnoj granici memorije (budući da adresa početka segmenta zapravo ima četiri nule nižeg reda, kao što se vidi na slici 7.4.2), odnosno na adresi koja je višekratnik 16. Ove važeće granice segmenta nazivaju se granicama paragrafa.

Imajte na umu da je uvođenje segmentacije prvenstveno posljedica činjenice da su interni registri procesora 16-bitni, a adresa fizičke memorije 20-bitna (16-bitna adresa omogućuje korištenje samo 64 KB memorije, što je jasno nedovoljno).

Predmemorija se nalazi između glavne memorije (RAM) i Središnja procesorska jedinica kako bi se smanjilo vrijeme provedeno na CPU pristupu OP-u.

Ideja cache memorije temelji se na predviđanju najvjerojatnijih CPU pristupa RAM-u. Najvjerojatniji podaci i upute kopiraju se u brzu predmemoriju s brzinom CPU-a prije nego što ih CPU zapravo iskoristi, tako da se podacima i uputama koje se trenutno koriste mogu brzo pristupiti, bez pribjegavanja RAM-u. Ovaj pristup temelji se na principu lokalnosti programa ili, kako se kaže, ugniježđenosti poziva, što znači da adrese uzastopnih poziva OP-u u pravilu čine kompaktnu grupu. Prilikom pristupa RAM-u, u predmemoriju se ne kopiraju pojedinačni podaci, već blokovi informacija, uključujući one podatke koji će se najvjerojatnije koristiti u CPU-u u narednim koracima rada. S tim u vezi, CPU više ne bira naknadne upute iz RAM-a, već iz brze cache memorije. Kada CPU treba pročitati ili zapisati neke podatke u RAM, prvo provjerava njihovu prisutnost u predmemoriji. Učinkovitost sustava predmemorije ovisi o veličini bloka i algoritmu programa.

glavna memorija

glavna memorija - uređaj za pohranu koji je izravno povezan s procesorom i dizajniran za pohranu izvršnih programa i podataka izravno uključenih u operacije. Ima dovoljnu brzinu, ali ograničen volumen. Glavna memorija je podijeljena na različite vrste, od kojih su glavne memorija s slučajnim pristupom (RAM) i memorija samo za čitanje (ROM) (slika 1.).

RAM je dizajniran za pohranjivanje informacija (programa i podataka) u koje su izravno uključene računalni proces u trenutnoj fazi rada.

RAM se koristi za primanje, pohranjivanje i izdavanje informacija. Upravo u njemu procesor "uzima" programe i početne podatke za obradu, zapisuje mu rezultate. Ova memorija je dobila naziv “RAM” jer radi vrlo brzo, tako da procesor ne mora puno čekati pri čitanju podataka iz memorije i zapisivanju u memoriju. Međutim, podaci koje sadrži spremaju se samo dok je računalo uključeno. Kada isključite računalo, sadržaj RAM-a se briše. Dakle, RAM je nestabilna memorija.

Riža. 1. Glavne vrste glavne memorije

Često se koristi oznaka RAM (memorija slučajnog pristupa, tj. memorija s nasumični pristup). Pod slučajnim pristupom podrazumijeva se mogućnost izravnog pristupa bilo kojoj (arbitrarnoj) zadanoj memorijskoj ćeliji, a vrijeme pristupa za bilo koju ćeliju je isto.

RAM se temelji na velikim integrirani krugovi koji sadrže matrice poluvodičkih elemenata za pohranu (japanke). Memorijski elementi nalaze se na sjecištu vertikalnih i horizontalnih guma matrice; snimanje i čitanje informacija provodi se primjenom električnih impulsa kroz one kanale matrice koji su spojeni na elemente koji pripadaju odabranoj memorijskoj ćeliji.

Ne samo sposobnost rada s programima koji zahtijevaju velike resurse, već i njegova izvedba ovisi o količini RAM-a koji je instaliran u računalu, budući da se u slučaju nedostatka memorije koristi kao njegov logički nastavak. HDD, vrijeme pristupa kojemu je neusporedivo veće. Osim količine RAM-a, na performanse računala utječe i njegova brzina te način razmjene podataka između mikroprocesora i memorije.

OP je implementiran na DRAM čipovima (dinamički OP), koji se u usporedbi s drugim vrstama memorije odlikuje niskom cijenom i visokim specifičnim kapacitetom, ali velikom potrošnjom energije i sporijim performansama. Svaki informacijski bajt (0 i 1) u DRAM-u pohranjen je kao napunjenost kondenzatora. Zbog prisutnosti struja propuštanja, punjenje kondenzatora mora se obnavljati u određenim intervalima. Zbog stalne potrebe za ažuriranjem, takva memorija se naziva dinamičkom. Regeneracija sadržaja memorije zahtijeva dodatno vrijeme, a bilježenje informacija tijekom regeneracije u memoriju nije dopušteno.

Cijena RAM-a u U posljednje vrijeme naglo pao (od ljeta 1995. do ljeta 1996. - više od 4 puta), pa su veliki zahtjevi mnogih programa i operativnih sustava za RAM s financijska točka vid je postao manje opterećujući.

Za ubrzanje pristupa RAM-u na brzim računalima koristi se stabilna cache memorija ultra velike brzine, koja se nalazi, takoreći, "između" mikroprocesora i RAM-a i pohranjuje kopije najčešće korištenih dijelova RAM-a . Kada mikroprocesor pristupi memoriji, najprije traži potrebne podatke iz cache memorije. Budući da je vrijeme pristupa cache memoriji nekoliko puta manje nego do konvencionalno pamćenje, a u većini slučajeva podaci potrebni za mikroprocesor već su pohranjeni u cache memoriju, prosječno vrijeme pristupa memoriji se smanjuje. Predmemorija je implementirana na SRAM (statički RAM) čip.

Za računala temeljena na Intel-386DX ili 80386SX dovoljna je veličina predmemorije od 64 KB, dok je dovoljno 128 KB. Računala temeljena na Intel-80486DX, DX2, DX4 i Pentium obično su opremljena s 256 KB cache memorije.

Mikroprocesori serije 486 i Pentium sadrže malu količinu interne cache memorije, pa se zbog jasnoće terminologije ponekad u tehničkoj literaturi cache memorija koja se nalazi na matičnoj ploči naziva predmemorija druge razine.

U mikroprocesoru Pentium Pro cache memorija druge razine sadržana je u jednom paketu sa samim procesorom (može se reći da je ugrađena u mikroprocesor).

Nije potrebno imati svu memoriju u kojoj se informacija mora mijenjati. Dio najviše važna informacija bolje ga je trajno čuvati u memoriji računala. Ova memorija se naziva trajnom. Podaci se tijekom izrade unose u trajnu memoriju. U pravilu se ti podaci ne mogu mijenjati, programi koji se izvršavaju na računalu mogu ih samo čitati. Ova vrsta memorije se obično naziva ROM (memorija samo za čitanje ili memorija samo za čitanje) ili ROM (Memorija samo za čitanje).

Računalo kompatibilno s IBM PC-om pohranjuje programe u trajnu memoriju za provjeru hardvera, računala, pokretanje učitavanja operativnog sustava (OS) i izvršavanje osnovne funkcije održavanje računalnih uređaja. Budući da se većina ovih programa bavi I/O uslugama, sadržaj trajne memorije se često naziva BIOS (Basic Input - Output System, ili osnovni ulazno-izlazni sustav).

Mnoga računala instaliraju BIOS na temelju FLASH memorije. Takvu memoriju mogu mijenjati programi, što vam omogućuje ažuriranje BIOS-a pomoću posebnih programa, bez zamjene matična ploča ili BIOS čipove.

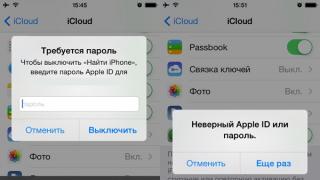

Sva računala osim vrlo starih također imaju program za konfiguraciju računala (SETUP) u BIOS-u. Omogućuje postavljanje nekih karakteristika računalnih uređaja (vrste video kontrolera, tvrdih diskova i floppy disk jedinica, neke i načina rada s RAM-om, traženje lozinke pri pokretanju itd.). Obično se konfiguracijski program poziva kada korisnik pritisne određenu tipku ili kombinaciju tipki (najčešće tipku Del) tijekom podizanja sustava.

Kapacitet FLASH memorije od 32 KB do 2 MB, vrijeme pristupa čitanju 0,06 µs, vrijeme pisanja po bajtu približno 10 µs; FLASH memorija je nepromjenjiva memorija.

Osim obične RAM-a i trajne memorije, računalo ima i malu površinu memorije za pohranjivanje postavki konfiguracije računala. Često se naziva CMOS memorija jer se ova memorija obično implementira pomoću CMOS (komplementarni metal-oksidni poluvodič) tehnologije, koja ima niska potrošnja energije. Sadržaj CMOS memorije se ne mijenja kada je računalo isključeno jer za napajanje koristi posebnu bateriju.

Dakle, kapacitet glavne memorije sastoji se od milijuna pojedinačnih memorijskih ćelija s kapacitetom od 1 bajta svaka. Ukupni kapacitet glavne memorije modernih računala obično se kreće od 1 do 4 GB. Kapacitet RAM-a je jedan do dva reda veličine veći od kapaciteta ROM-a: ROM zauzima do 2 MB na novim matičnim pločama), ostalo je RAM.

Tema 3.1 Organizacija izračuna u računalni sustavi Oh

Namjena i karakteristike zrakoplova. Organizacija proračuna u računalnim sustavima. Računalo paralelno djelovanje, koncepti tijeka naredbi i toka podataka. sustavi asocijacija. Matrični sustavi. Računalni cjevovod. Cjevovod naredbi, cjevovod podataka. Superskalarizacija.

Učenik mora

znati:

Koncept tijeka naredbi;

Koncept protoka podataka;

Vrste računalnih sustava;

Arhitektonske značajke računalnih sustava

Računalni sustavi

Računalni sustav(Sunce)- skup međusobno povezanih i međusobno povezanih procesora ili računala, periferna oprema I softver, dizajniran za prikupljanje, pohranu, obradu i distribuciju informacija.

Stvaranje Oružanih snaga ima sljedeće glavne ciljeve:

Poboljšanje performansi sustava ubrzavanjem procesa obrade podataka;

Poboljšanje pouzdanosti i pouzdanosti izračuna;

Pružanje korisniku dodatne usluge itd.

Tema 3.2

Klasifikacija zrakoplova ovisno o broju naredbi i tokova podataka: OKOD (SISD), OKMD (SIMD), MISD (MISD), MKMD (MIMD).

Klasifikacija višeprocesorskih računalnih sustava s različitim načinima implementacije dijeljene memorije: UMA, NUMA, COMA. Usporedne karakteristike, značajke hardvera i softvera.

Klasifikacija višestrojnih zrakoplova: MPP, NDW i COW. Namjena, karakteristike, značajke.

Primjeri sunca različite vrste. Prednosti i nedostaci različitih vrsta računalnih sustava.

Klasifikacija računalnih sustava

Posebnost CS-a u odnosu na klasična računala je prisutnost u njemu nekoliko kalkulatora koji implementiraju paralelna obrada .

Paralelnost izvođenja operacija značajno povećava brzinu sustava; može značajno povećati pouzdanost (ako jedna komponenta sustava otkaže, druga može preuzeti njegovu funkciju), kao i pouzdanost sustava, ako se operacije dupliciraju i uspoređuju rezultati.

Računalni sustavi mogu se podijeliti u dvije grupe:

· višestrojna ;

· višeprocesor .

Višestrojni računalni sustav sastoji se od nekoliko pojedinačnih računala. Svako računalo u višestrojnom sustavu ima klasičnu arhitekturu, a takav sustav ima dosta široku primjenu. Međutim, učinak korištenja takvog računalnog sustava može se postići samo rješavanjem problema koji ima posebnu strukturu: mora se podijeliti na onoliko labavo povezanih podzadataka koliko ima računala u sustavu.

Višeprocesorska arhitektura podrazumijeva prisutnost nekoliko procesora u računalu, tako da se mnogi tokovi podataka i mnogi tokovi instrukcija mogu organizirati paralelno. Dakle, nekoliko fragmenata jednog zadatka može se izvršiti istovremeno. Prednost u brzini višeprocesorskih računalnih sustava u odnosu na jednoprocesorske je očita.

Nedostatak je mogućnost konfliktne situacije kada više procesora pristupa istom memorijskom području.

Značajka višeprocesorskih računalnih sustava je prisutnost zajedničkog RAM-a kao zajednički resurs(Slika 11).

Slika 11 - Arhitektura višeprocesorskog računalnog sustava

Flynn klasifikacija

Među svim razmatranim sustavima klasifikacije zrakoplova najviše se koristi klasifikacija koju je 1966. predložio M. Flynn. Temelji se na koncept protoka , što se shvaća kao slijed naredbi ili elemenata podataka koje obrađuje procesor. Ovisno o broju tokova naredbi i tokova podataka, Flynn razlikuje 4 klase arhitektura:

· OKOD – single command stream - single data stream. To uključuje klasične von Neumannove VM-ove. Pipelining nije bitan, stoga i 6600 VM sa skalarnim funkcionalnim jedinicama i 7600 s cjevovodnim spadaju u OKOD klasu.

· MKOD – višestruki tok naredbi - jedan tok podataka. U ovoj arhitekturi, više procesora obrađuje isti tok podataka. Primjer bi bio zrakoplov na čije procesore se isporučuje iskrivljeni signal, a svaki od procesora obrađuje taj signal koristeći svoj vlastiti algoritam filtriranja. Međutim, ni Flynn ni drugi računalni arhitekti još nisu mogli zamisliti stvarni zrakoplov izgrađen na ovaj princip. Brojni istraživači upućuju transportne sustave u ovu klasu, ali to nije naišlo na konačno priznanje. Prazan razred ne bi se trebao smatrati nedostatkom Flynnove klasifikacije. Takve nastave mogu postati korisne u razvoju novih koncepata u teoriji i praksi konstrukcije zrakoplova.

· OKMD - jedan tok naredbi - mnogo tokova podataka - naredbe izdaje jedan upravljački procesor, a izvršavaju se istovremeno na svim procesorima za obradu na lokalnim podacima tih procesora. SIMD (jedna instrukcija - više podataka)

· MKMD - mnogi tokovi naredbi - mnogi tokovi podataka - skup računala koja rade prema svojim programima sa svojim izvornim podacima. MIMD (više instrukcija - više podataka)

Flynnova klasifikacijska shema najčešća je u početnoj procjeni zrakoplova, jer vam odmah omogućuje procjenu osnovnog principa sustava. Međutim, Flynnova klasifikacija također ima očite nedostatke: na primjer, nemogućnost da se neke arhitekture nedvosmisleno dodijele određenoj klasi. Drugi nedostatak je pretjerano zasićenje MIMD klase.

Postojeći računalni sustavi MIMD klase čine tri podklase: simetrični multiprocesori (SMP) , grozdovima I masivno paralelni sustavi (MPP). Ova se klasifikacija temelji na strukturno-funkcionalnom pristupu.

Simetrični multiprocesori sastoje se od skupa procesora koji imaju iste mogućnosti pristupa memoriji i vanjskim uređajima i rade pod istim operativnim sustavom (OS). poseban slučaj SMP je skraćenica za jednoprocesorska računala. Svi SMP procesori imaju zajedničku memoriju s jednim adresnim prostorom.

Korištenje SMP osigurava sljedeće mogućnosti:

• skaliranje aplikacije uz niske početne cijene, primjenom bez transformacije aplikacija na novi, produktivniji hardver;

Izrada aplikacija u poznatom softverska okruženja;

isto vrijeme pristupa cijeloj memoriji;

mogućnost slanja poruka s velikom propusnošću;

Podrška za koherentnost skupa predmemorije i blokova glavne memorije, nedjeljive operacije sinkronizacije i blokiranja.

klaster sustav formirana od modula povezanih komunikacijskim sustavom ili zajedničkim uređajima vanjska memorija kao što su nizovi diskova.

Veličina klastera varira od nekoliko modula do nekoliko desetaka modula.

Unutar dijeljene i distribuirane memorije implementirano je nekoliko modela arhitektura memorijskog sustava. Slika 12 prikazuje klasifikaciju takvih modela koji se koriste u računalnim sustavima klase MIMD (to vrijedi i za klasu SIMD).

Slika 12 - Klasifikacija modela memorijske arhitekture računalnih sustava

U sustavima iz zajednička memorija svi procesori imaju jednak pristup istom adresnom prostoru. Jedna memorija može se izgraditi kao jednoblok ili modularna, ali se obično prakticira druga opcija.

Računalni sustavi sa zajedničkom memorijom, gdje se pristup memoriji bilo kojeg procesora obavlja jednoliko i traje isto vrijeme, nazivaju se sustavi s ujednačenim pristupom memoriji a skraćeno su UMA (Uniform Memory Access). Ovo je najčešća memorijska arhitektura paralelnog VS-a sa zajedničkom memorijom.

Tehnički, UMA sustavi pretpostavljaju prisutnost čvora koji povezuje svaki od njih P procesora sa svakim T memorijski moduli. Najjednostavniji način za izradu takvog zrakoplova je kombiniranje nekoliko procesora (P i.) s jednom memorijom (M P) pomoću zajednički autobus- prikazano na slici 12a . U ovom slučaju, međutim, samo jedan od procesora može komunicirati na sabirnici u bilo kojem trenutku, odnosno procesori se moraju natjecati za pristup sabirnici. Kada procesor R i , dohvaća instrukciju iz memorije, drugih procesora R j(i ≠ j) morate pričekati dok se guma ne oslobodi. Ako su u sustavu samo dva procesora, oni mogu raditi s gotovo maksimalnom izvedbom jer se njihov pristup sabirnici može ispreplitati: dok jedan procesor dekodira i izvršava instrukciju, drugi može slobodno koristiti sabirnicu za dohvaćanje sljedeće instrukcije. iz sjećanja. Međutim, kada se doda treći procesor, performanse počinju padati. Kada je na sabirnici deset procesora, krivulja performansi sabirnice (slika 12b) postaje horizontalna, tako da dodavanje 11. procesora ne poboljšava performanse. Donja krivulja na ovoj slici ilustrira činjenicu da memorija i sabirnica imaju fiksnu širinu pojasa determiniranu kombinacijom vremena memorijskog ciklusa i protokola sabirnice, au zajedničkom višeprocesorskom sustavu sabirnice ta se širina pojasa dijeli na više procesora. Ako je ciklus procesora duži od ciklusa memorije, mnogi procesori se mogu spojiti na sabirnicu. Međutim, zapravo je procesor obično mnogo brži od memorije, pa se ova shema ne koristi široko.

Alternativni način izgradnja višeprocesorskog VS-a sa zajedničkom memorijom na temelju UMA prikazana je na slici 13c . Ovdje je sabirnica zamijenjena prekidačem koji usmjerava zahtjeve procesora na jedan od nekoliko memorijskih modula. Iako postoji više memorijskih modula, svi su dio jednog virtualnog adresnog prostora. Prednost ovog pristupa je u tome što preklopnik može poslužiti više zahtjeva paralelno. Svaki procesor može se spojiti na vlastiti memorijski modul i pristupiti mu maksimalnom dopuštenom brzinom. Do sukoba između procesora može doći kada pokušavate pristupiti istom memorijskom modulu u isto vrijeme. U tom slučaju samo jedan procesor dobiva pristup, a ostali su blokirani.

Nažalost, UMA arhitektura nije dobro skalirana. Najčešći sustavi sadrže 4-8 procesora, mnogo rjeđe 32-64 procesora. Osim toga, takvi se sustavi ne mogu klasificirati kao otporan na greške, budući da kvar jednog procesora ili memorijskog modula povlači kvar cijelog zrakoplova.

Slika 13 - Zajednička memorija:

a) kombiniranje procesora koji koriste sabirnicu i sustava s lokalnim predmemorijama;

b) performanse sustava kao funkcija broja procesora na sabirnici;

c) višeprocesorski CS sa zajedničkom memorijom koja se sastoji od pojedinačni moduli

Drugi pristup izgradnji zrakoplova sa zajedničkom memorijom je neujednačen pristup memoriji , koji se naziva NUMA (Neuniformni pristup memoriji). Ovdje se, kao i prije, pojavljuje jedan adresni prostor, ali svaki procesor ima lokalnu memoriju. Procesor izravno pristupa vlastitoj lokalnoj memoriji, što je mnogo brže od pristupa udaljenoj memoriji putem prekidača ili mreže. Takav sustav može se nadopuniti globalnom memorijom, u kojem slučaju lokalni uređaji za pohranu igraju ulogu brze cache memorije za globalnu memoriju. Takva shema može poboljšati performanse zrakoplova, ali ne može beskonačno odgoditi izjednačavanje izravnih performansi. Ako svaki procesor ima lokalnu predmemoriju (slika 13a), postoji velika vjerojatnost (p> 0.9) da se tražena naredba ili podaci već nalaze u lokalnoj memoriji. Razumna vjerojatnost pogađanja lokalne memorije značajno smanjuje broj procesorskih pristupa globalnoj memoriji i tako dovodi do povećanja učinkovitosti. Mjesto prijeloma krivulje performansi (gornja krivulja na slici 13b ), što odgovara točki u kojoj je dodavanje procesora još uvijek učinkovito, sada se pomiče u regiju s 20 procesora, a točka u kojoj krivulja postaje horizontalna u regiju s 30 procesora.

Kao dio koncepta NUMA implementirano je nekoliko različitih pristupa, označenih skraćenicama KOMA, CC-NUMA I NCC-NUMA.

U arhitektura samo predmemorije (COMA, Cache Only Memory Architecture) lokalna memorija svakog procesora izgrađena je kao velika cache memorija za brzi pristup iz "njegovog" procesora. Predmemorije svih procesora zajednički se tretiraju kao globalna memorija sustava. Ne postoji stvarna globalna memorija. Glavna značajka SOMA koncepta izražena je u dinamici. Ovdje podaci nisu statički vezani za određeni memorijski modul i nemaju jedinstvenu adresu koja ostaje nepromijenjena tijekom cijelog životnog vijeka varijable. U COMA arhitekturi podaci se prenose u cache memoriju procesora koji ih je zadnji zatražio, dok varijabla nije fiksirana jedinstvenom adresom i može se u bilo kojem trenutku smjestiti u bilo koju fizičku ćeliju. Prijenos podataka iz jedne lokalne predmemorije u drugu ne zahtijeva sudjelovanje operativnog sustava u ovom procesu, ali uključuje složen i skup hardver za upravljanje memorijom. Organizirati takav režim, tzv direktorije predmemorije . Također imajte na umu da se posljednja kopija stavke nikada ne uklanja iz predmemorije.

Budući da se podaci premještaju u lokalnu predmemoriju vlasničkog procesora u arhitekturi COMA, takvi AN-ovi imaju značajnu prednost u izvedbi u odnosu na druge NUMA arhitekture. S druge strane, ako dva procesora zahtijevaju jednu varijablu ili dvije različite varijable pohranjene u istoj liniji iste predmemorije, ta linija predmemorije mora se pomicati naprijed-natrag između procesora pri svakom pristupu podacima. Takvi učinci mogu ovisiti o detaljima dodjele memorije i dovesti do nepredvidivih situacija.

Model cache-koherentan pristup heterogenoj memoriji (CC-NUMA, Cache Coherent Non-Uniform Memory Architecture) bitno se razlikuje od COMA modela. CC-NUMA sustav ne koristi cache memoriju, već običnu fizički distribuiranu memoriju. Nema kopiranja stranica ili podataka između memorijskih mjesta. Ne postoji softverski implementirano prosljeđivanje poruka. Postoji samo jedna memorijska kartica, s dijelovima koji su fizički povezani bakreni kabel, i "pametni" hardver. Koherentnost hardverske predmemorije znači da nije potreban softver za pohranjivanje više kopija ažuriranih podataka ili njihovo prijenos. Sve to rješava hardverska razina. Pristup lokalnim memorijskim modulima u različitim čvorovima sustava može se obavljati istovremeno i brži je nego udaljenim memorijskim modulima.

Razlika između modela i cache-inkoherentan pristup heterogenoj memoriji (NCC-NUMA, Non-Cache Coherent Non-Uniform Memory Architecture) od CC-NUMA očito je iz imena. Arhitektura memorije pretpostavlja jedan adresni prostor, ali ne osigurava globalnu konzistentnost podataka na razini hardvera. Korištenje takvih podataka u potpunosti je odgovornost softvera (aplikacija ili kompilatora). Unatoč ovoj okolnosti, koja se čini nedostatkom arhitekture, pokazuje se vrlo korisnom u poboljšanju performansi računalnih sustava s memorijskom arhitekturom tipa DSM, koja se razmatra u odjeljku "Modeli distribuirane memorijske arhitekture".

Općenito se nazivaju zrakoplovi NUMA zajedničke memorije arhitekture s virtualnom zajedničkom memorijom (virtualne dijeljene memorije arhitekture). Ova vrsta arhitekture, posebice CC-NUMA, nedavno se smatra neovisnom i prilično obećavajućom vrstom računalnih sustava klase M1MD.

Modeli arhitektura distribuirane memorije. U distribuiranom memorijskom sustavu, svaki procesor ima vlastitu memoriju i može je samo adresirati. Neki autori ovu vrstu sustava nazivaju višestrojnim zrakoplovom odn višeračunala , naglašavajući činjenicu "da su blokovi od kojih je izgrađen sustav sami mali računalni sustavi s procesorom i memorijom. Modeli distribuiranih memorijskih arhitektura obično se nazivaju arhitektura bez izravne pristup udaljenoj memoriji (NORMA, Nema pristupa daljinskoj memoriji). Ovaj naziv dolazi iz činjenice da svaki procesor ima pristup samo svojoj lokalnoj memoriji. Pristup udaljenoj memoriji (lokalna memorija drugog procesora) moguć je samo razmjenom poruka s procesorom koji posjeduje adresabilnu memoriju.

Takva organizacija ima niz prednosti. Prvo, kada se pristupa podacima, nema konkurencije za sabirnicu ili sklopke: svaki procesor može u potpunosti koristiti propusnost komunikacijskog puta s vlastitom lokalnom memorijom. Drugo, nepostojanje zajedničke sabirnice znači da ne postoje povezana ograničenja za broj procesora: veličina sustava ograničena je samo mrežom koja kombinira procesore. Treće, otklanja se problem koherentnosti predmemorije. Svaki procesor ima pravo samostalno mijenjati svoje podatke, bez brige o usklađivanju kopija podataka u vlastitoj lokalnoj predmemoriji s predmemorijama drugih procesora.

Učenik mora

znati:

klasifikacija zrakoplova;

Primjeri zrakoplova raznih tipova.

biti u mogućnosti:

- odabrati vrstu računalnog sustava u skladu s problemom koji se rješava.

©2015-2019 stranica

Sva prava pripadaju njihovim autorima. Ova stranica ne tvrdi autorstvo, ali pruža besplatno korištenje.

Datum izrade stranice: 22.07.2016

Poglavlje 11

Organizacija računalnu memoriju sustava

U računalnim sustavima koji kombiniraju mnoge paralelne procesore ili strojeve, problem pravilne organizacije memorije jedan je od najvažnijih. Razlika između brzine procesora i memorije oduvijek je bila kamen spoticanja u VM-ovima s jednim procesorom. Višeprocesorska priroda CS-a dovodi do drugog problema - problema istovremenog pristupa memoriji od strane više procesora.

Ovisno o tome kako je organizirana memorija višeprocesorskih (višestrojnih) sustava, razlikuju se računalni sustavi sa zajedničkom memorijom (shared memory) i računalni sustavi s distribuiranom memorijom (distributed memory). U sustavi zajedničke memorije(često se naziva zajednička ili dijeljena memorija) VM se tretira kao zajednički resurs, a svaki od procesora ima puni pristup cijelom adresnom prostoru. Sustavi sa zajedničkom memorijom nazivaju se snažno povezan(usko povezani sustavi). Slična konstrukcija računalnih sustava odvija se i u klasi SIMD iu klasi MIMD. Ponekad se, kako bi se naglasila ova okolnost, uvode posebne podklase, koje označavaju skraćenicama SM-SIMD (Shared Memory SIMD) i SM-MIMD (Shared Memory MIMD).

U varijanti distribuiranu memoriju svaki od procesora dobiva svoju memoriju. Procesori se spajaju u mreže i mogu po potrebi razmjenjivati podatke pohranjene u njihovoj memoriji, prenoseći jedni drugima tzv poruke. Ova vrsta zrakoplova tzv labavo spojeni(labavo spojeni sustavi). Slab srodni sustavi također se javljaju iu klasi SIMD iu klasi MIMD, a ponekad da naglasim ovu značajku, uvesti podklase DM-SIMD (Distributed Memory SIMD) i DM-MIMD (Distributed Memory MIMD).

U nekim slučajevima nazivaju se računalni sustavi dijeljene memorije multiprocesori, i sustavi s distribuiranom memorijom - višeračunala.

Razlika između dijeljene i distribuirane memorije je razlika u strukturi virtualne memorije, odnosno kako memorija izgleda sa strane procesora. Fizički se gotovo svaki memorijski sustav dijeli na samostalne komponente kojima se može samostalno pristupiti. Ono što dijeli dijeljenu memoriju od distribuirane memorije je način na koji memorijski podsustav tumači adresu ćelije primljenu od procesora. Na primjer, pretpostavimo da procesor izvršava naredbu load RO, i koja znači "Učitaj registar R0 sa sadržajem ćelije i". U slučaju dijeljene memorije, i je globalna adresa i ukazuje na isto mjesto za bilo koji procesor. U distribuirani sustav sjećanje jesam lokalna adresa Ako dva procesora izvršavaju opterećenje instrukcija RO, i, tada svaki od njih pristupa i-ta ćelija u vašem lokalnom sjećanju, odnosno da različite stanice, a različite vrijednosti mogu se učitati u registre R0.

Programer mora uzeti u obzir razliku između dvaju memorijskih sustava, jer ona određuje način interakcije dijelova paraleliziranog programa. U varijanti sa zajedničkom memorijom, dovoljno je stvoriti strukturu podataka u memoriji i proslijediti reference na tu strukturu u paralelno korištene potprograme. U sustavu distribuirane memorije potrebno je imati kopiju zajedničkih podataka u svakoj lokalnoj memoriji. Te se kopije stvaraju ugrađivanjem zajedničkih podataka u poruke poslane drugim procesorima.

Memorija iz izmjenjivanje adrese

Fizički se memorija računalnog sustava sastoji od nekoliko modula (banka), a bitno je pitanje kako se u ovom slučaju raspoređuje adresni prostor (skup svih adresa koje procesor može formirati). Jedan od načina dodjeljivanja virtualnih adresa memorijskim modulima je podjela adresnog prostora na uzastopne blokove. Ako je sjećanje P banke, zatim ćelija s adresom i tijekom cijepanja blokova bit će u banci s brojem ja/n. U sustavu isprepletena memorija(interleaved memory) uzastopne adrese nalaze se u različitim bankama: ćelija s adresom i nalazi se u banci s brojem i mod P. Neka se, na primjer, memorija sastoji od četiri banke, svaka po 256 bajtova. U shemi blok adresiranja, prva banka će biti dodijeljena virtualne adrese 0-255, drugi - 256-511, itd. U isprepletenoj shemi, uzastopne ćelije u prvoj banci imat će virtualne adrese 0, 4, 8, .... u drugoj banci - 1, 5, 9, itd. (Slika 11.1, a).

Distribucija adresnog prostora po modulima omogućuje istovremenu obradu zahtjeva za pristup memoriji, ako odgovarajuće adrese pripadaju različitim bankama, procesor može zatražiti pristup ćeliji u jednom od ciklusa i a u sljedećoj petlji - do ćelije j. Ako ja ij su u različitim bankama, informacije će se prenositi u uzastopnim ciklusima. Ovdje se ciklus odnosi na ciklus procesora, dok puni memorijski ciklus traje nekoliko ciklusa procesora. Dakle, u ovom slučaju procesor ne mora čekati dok se ne završi puni ciklus pristupa ćeliji. i. Razmatrana tehnika omogućuje povećanje propusnost: ako se memorijski sustav sastoji od

https://pandia.ru/text/78/264/images/image002_61.jpg" width="62" height="15"> Interval između elemenata naziva se korak po indeks ili "Korak"(korakom). Jedan od zanimljive aplikacije ovo svojstvo može poslužiti kao pristup matricama. Ako je indeksni korak za jedan veći od broja redaka u matrici, jedan zahtjev za pristup memoriji će vratiti sve dijagonalne elemente matrice (slika 11.1b). Programerova je odgovornost osigurati da se svi ekstrahirani elementi matrice nalaze u različitim bankama.

Modeli memorijske arhitekture računalnih sustava

Unutar dijeljene i distribuirane memorije implementirano je nekoliko modela arhitektura memorijskog sustava.

DIV_ADBLOCK84">

Riža. 11.3. Zajednička memorija: a - kombiniranje procesora pomoću sabirnice; b - sustav s lokalnim predmemorijama; u- performanse sustava kao funkcija broja procesora na sabirnici; d - višeprocesorski VS sa zajedničkom memorijom koja se sastoji od pojedinačnih modula

Na sl. 11.3, G. Ovdje je šiljak zamijenjen prekidačem koji usmjerava zahtjeve procesora na jedan od nekoliko memorijskih modula. Iako postoji više memorijskih modula, svi su dio jednog virtualnog adresnog prostora. Prednost ovog pristupa je u tome što preklopnik može poslužiti više zahtjeva paralelno. Svaki procesor može se spojiti na vlastiti memorijski modul i pristupiti mu maksimalnom dopuštenom brzinom. Do sukoba između procesora može doći kada pokušavate pristupiti istom memorijskom modulu u isto vrijeme. U tom slučaju samo jedan procesor dobiva pristup, a ostali su blokirani.

Nažalost, UMA arhitektura nije dobro skalirana. Najčešći sustavi sadrže 4-8 procesora, mnogo rjeđe 32-64 procesora. Osim toga, takvi se sustavi ne mogu klasificirati kao otporni na greške, budući da kvar jednog procesora ili memorijskog modula povlači kvar cijelog zrakoplova.

Drugi pristup izgradnji zrakoplova sa zajedničkom memorijom je heterogeni pristup memoriji, koji se naziva NUM A (Neuniformni pristup memoriji). Ovo još uvijek ima jedan adresni prostor, ali svaki procesor ima lokalnu memoriju. Procesor izravno pristupa vlastitoj lokalnoj memoriji, što je mnogo brže od pristupa udaljenoj memoriji putem prekidača ili mreže. Takav sustav može se nadopuniti globalnom memorijom, tada lokalni uređaji za pohranu igraju ulogu brze cache memorije za globalnu memoriju. Takva shema može poboljšati performanse zrakoplova, ali ne može na neodređeno vrijeme odgoditi izravno izjednačavanje performansi. Ako svaki procesor ima lokalnu predmemoriju (slika 11.3.6), postoji velika vjerojatnost (p > 0.9) da se tražena naredba ili podaci već nalaze u lokalnoj memoriji. Razumna vjerojatnost pogađanja lokalne memorije značajno smanjuje broj pristupa procesoru do globalno pamćenje i tako dovodi do povećanja učinkovitosti. Mjesto prijeloma krivulje performansi (gornja krivulja na slici 11.3, u), točka u kojoj je dodavanje procesora još uvijek učinkovito sada se pomiče u regiju s 20 procesora, a tanka linija gdje krivulja postaje horizontalna u regiju s 30 procesora.

Kao dio koncepta NUMA implementirano je nekoliko različitih pristupa, označenih skraćenicama SOMA,CC-NUMA I NCC-NUMA.

U arhitektura samo predmemorije(COMA, Cache Only Memory Architecture) lokalna memorija svakog procesora izgrađena je kao velika predmemorija za brzi pristup iz "njegovog" procesora. Predmemorije svih procesora zajednički se tretiraju kao globalna memorija sustava. Ne postoji stvarna globalna memorija. Glavna značajka SOMA koncepta izražena je u dinamici. Ovdje podaci nisu statički vezani za određeni memorijski modul i nemaju jedinstvenu adresu koja ostaje nepromijenjena tijekom cijelog životnog vijeka varijable. U COMA arhitekturi podaci se prenose u cache memoriju procesora koji ih je zadnji zatražio, dok varijabla nije fiksirana jedinstvenom adresom i može se u bilo kojem trenutku smjestiti u bilo koju fizičku ćeliju. Prijenos podataka iz jedne lokalne predmemorije u drugu ne zahtijeva sudjelovanje operativnog sustava u ovom procesu, ali uključuje složen i skup hardver za upravljanje memorijom. Organizirati takav režim, tzv direktorije predmemorije. Također imajte na umu da se posljednja kopija stavke nikada ne uklanja iz predmemorije.

Budući da arhitektura COMA premješta podatke u lokalnu predmemoriju vlasničkog procesora, takvi EC-ovi imaju značajnu prednost u performansama u odnosu na druge arhitekture NUM A. S druge strane, ako se jedna varijabla ili dvije različite varijable pohranjuju u istom redu istog cache , zahtijevaju dva procesora, ova linija predmemorije mora se pomicati naprijed-nazad između procesora pri svakom pristupu podacima. Takvi učinci mogu ovisiti o detaljima dodjele memorije što dovodi do nepredvidivih situacija.

Model cache-koherentan pristup heterogenoj memoriji(CC-NUMA, Cache Coherent Non-Uniform Memory Architecture) bitno se razlikuje od COMA modela. CC-NUMA sustav ne koristi cache memoriju, već običnu fizički distribuiranu memoriju. Nema kopiranja stranica ili podataka između memorijskih mjesta. Ne postoji softverski implementirano prosljeđivanje poruka. Postoji samo jedna memorijska kartica, s dijelovima fizički spojenim bakrenim kabelom i "pametnim" hardverom. Koherentnost hardverske predmemorije znači da nije potreban softver za pohranjivanje više kopija ažuriranih podataka ili njihovo prijenos. Sve to rješava hardverska razina. Pristup lokalnim memorijskim modulima u različitim čvorovima sustava može se obavljati istovremeno i brži je nego udaljenim memorijskim modulima.

Razlika između modela i cache-inkoherentan pristup heterogenoj memoriji(NCC-NUMA, Non-Cache Coherent Non-Uniform Memory Architecture) od CC-NUMA očito je iz imena. Arhitektura memorije pretpostavlja jedan adresni prostor, ali ne osigurava globalnu konzistentnost podataka na razini hardvera. Korištenje takvih podataka u potpunosti je odgovornost softvera (aplikacija ili kompilatora). Unatoč ovoj okolnosti, koja se čini nedostatkom arhitekture, pokazuje se vrlo korisnom u poboljšanju performansi računalnih sustava s memorijskom arhitekturom tipa DSM, koja se razmatra u odjeljku "Modeli distribuirane memorijske arhitekture".

Općenito se nazivaju zrakoplovi NUMA zajedničke memorije arhitekture s virtualnom zajedničkom memorijom(virtualne dijeljene memorije arhitekture). Ova vrsta arhitekture, posebice CC-NUMA, nedavno se smatra neovisnom i prilično obećavajućom vrstom računalnih sustava MIMD klase, stoga će se takav CS detaljnije raspravljati u nastavku.

Modeli arhitektura distribuirane memorije

U distribuiranom memorijskom sustavu, svaki procesor ima vlastitu memoriju i može je samo adresirati. Neki autori ovu vrstu sustava nazivaju zrakoplovi s više strojeva ili višeračunala, ističući činjenicu da su građevni blokovi sustava sami po sebi mali računalni sustavi s procesorom i memorijom. Modeli arhitektura s distribuiranom memorijom obično se nazivaju arhitekture bez izravnog pristupa udaljenoj memoriji(NORMA, Nema pristupa daljinskoj memoriji). Ovaj naziv dolazi iz činjenice da svaki procesor ima pristup samo svojoj lokalnoj memoriji. Pristup udaljenoj memoriji (lokalna memorija drugog procesora) moguć je samo razmjenom poruka s procesorom koji posjeduje adresabilnu memoriju.

Takva organizacija ima niz prednosti. Prvo, pri pristupu podacima nema konkurencije za sabirnicu ili sklopke - svaki procesor može u potpunosti koristiti propusnost komunikacijskog puta sa svojom vlastitom lokalnom memorijom. Drugo, nepostojanje zajedničke sabirnice znači da ne postoje povezana ograničenja za broj procesora: veličina sustava ograničena je samo mrežom koja kombinira procesore. Treće, otklanja se problem koherentnosti predmemorije. Svaki procesor ima pravo samostalno mijenjati svoje podatke, bez brige o usklađivanju kopija podataka u vlastitoj lokalnoj predmemoriji s predmemorijama drugih procesora.

Glavni nedostatak distribuirane memorije CS je složenost razmjene informacija između procesora. Ako jedan od procesora treba podatke iz memorije drugog procesora, mora razmjenjivati poruke s tim procesorom. To rezultira dvije vrste troškova:

· Potrebno je vrijeme za formiranje i prosljeđivanje poruke od jednog! procesor drugome;

· Da bi odgovorio na poruke od drugih procesora, procesor primatelj mora primiti zahtjev za prekidom i izvršiti rutinu rukovanja prekidom.

Struktura sustava s distribuiranom memorijom prikazana je na slici 1. 11.4. U lijevo! dijelovi (slika 11.4, ali) prikazan je jedan procesni element (PE). Uključuje) sam procesor (P), lokalnu memoriju (M) i dva ulazno/izlazna kontrolera (Ko i CD na desnoj strani (Sl. 11.4, b) prikazan je četveroprocesorski sustav koji ilustrira kako se poruke šalju s jednog procesora na drugi. U odnosu na svaki PE, svi ostali elementi procesora mogu se smatrati jednostavno ulaznim/izlaznim uređajima. Za slanje poruke drugom PE, procesor formira podatkovni blok u svojoj lokalnoj memoriji i obavještava ga lokalni kontrolor o potrebi prijenosa informacija u vanjski uređaj. Mreža za međupovezivanje prosljeđuje ovu poruku prijemnom I/O kontroleru PE primatelja. Potonji pronalazi mjesto za poruku u vlastitoj lokalnoj memoriji i obavještava izvorni procesor da je poruka primljena.

DIV_ADBLOCK89">

Zanimljiva varijanta distribuiranog memorijskog sustava je; model distribuirana zajednička memorija(DSM, Distribute Shared Memory), također poznat pod drugim imenom arhitektura s heterogenimsoftver za pristup memoriji i koherentnost(SC-NUMA, softversko-koherentna neuniformna memorijska arhitektura). Ideja ovog modela je da se VS, fizički kao sustav s distribuiranom memorijom, predstavlja korisniku kao sustav sa zajedničkom memorijom zahvaljujući operativnom sustavu. To znači da operativni sustav korisniku nudi jedan adresni prostor, unatoč činjenici da je stvarni pristup memoriji “stranog” računala VS i dalje omogućen razmjenom poruka.

Višeprocesorkoherentnost cache- memorija

Višeprocesorski sustav dijeljene memorije sastoji se od dva ili više neovisnih procesora, od kojih svaki obavlja bilo koji dio veliki program ili neovisni program. Svi procesori pristupaju uputama i podacima pohranjenim u zajedničkoj glavnoj memoriji. Budući da je memorija zajednički resurs, dolazi do sukoba između procesora kada joj se pristupi, što rezultira povećanjem prosječne latencije pristupa memoriji. Kako bi se smanjilo ovo kašnjenje, svaki procesor dobiva lokalnu predmemoriju koja, služeći pristupima lokalnoj memoriji, u mnogim slučajevima sprječava potrebu za pristupom zajedničkoj glavnoj memoriji. Zauzvrat, opremanje svakog procesora lokalnom cache memorijom dovodi do tzv problem koherencije ili pružanje premacache memorija. Prema , sustav je koherentan ako svaka operacija čitanja na bilo koju adresu koju izvrši bilo koji od procesora vraća vrijednost unesenu tijekom posljednje operacije pisanja na ovu adresu, bez obzira na to koji je od procesora zadnji napisao.

U svom najjednostavnijem obliku, problem koherencije predmemorije može se objasniti na sljedeći način (slika 11.5). Neka dva procesora Rg i Rg su spojeni na zajedničku memoriju preko sabirnice. Prvo, oba procesora čitaju varijablu X. Kopije blokova koji sadrže ovu varijablu prenose se iz glavne memorije u lokalne predmemorije oba procesora (slika 11.5, ali). Zatim procesor Pt izvodi operaciju povećanja vrijednosti varijable x po jedinici. Budući da je kopija varijable već u predmemoriji procesora, dogodit će se pogodak u predmemoriji i vrijednost će se promijeniti samo u predmemoriji 1. Ako procesor P2 sada ponovno izvrši operaciju čitanja X, tada će se također dogoditi pogodak u predmemoriju i P2 će dobiti "staru" vrijednost pohranjenu u svojoj predmemoriji x(Slika 11.5, b).

Održavanje konzistentnosti zahtijeva da kada se element podataka promijeni od strane jednog od procesora, odgovarajuće promjene se izvrše u predmemoriji drugih procesora, gdje se nalazi kopija promijenjenog elementa podataka, kao iu zajedničkoj memoriji. Sličan problem se, inače, javlja u jednoprocesorskim sustavima, gdje postoji nekoliko razina cache memorije. Ovdje je potrebno uskladiti sadržaje predmemorije različitih razina.

Postoje dva pristupa rješavanju problema koherentnosti: softverski i hardverski. Neki sustavi koriste strategije koje kombiniraju oba pristupa.

Softver načine rješenjaProblemi koherentnost

Softverske tehnike za rješavanje problema koherentnosti omogućuju bez njih dodatna oprema ili ga minimizirati.

ProtokolBerkeley. Berkeley protokol je primijenjen na višeprocesorski sustav Berkeley baziran na RISC procesorima.

Opći troškovi koji nastaju zbog promašaja predmemorije smanjeni su idejom o vlasništvu linije predmemorije implementiranom u ovom protokolu. Obično se glavna memorija smatra vlasnikom prava na sve blokove podataka. Prije izmjene sadržaja retka u njegovoj predmemoriji, procesor mora steći vlasništvo nad zadanu liniju. Ta se prava stječu posebnim operacijama čitanja i pisanja. Ako pri pristupu bloku čiji je vlasnik ovaj trenutak nije glavna memorija, dolazi do promašaja predmemorije, procesor koji posjeduje red sprječava čitanje iz glavne memorije i opskrbljuje procesor koji je tražio podatke iz njegove lokalne predmemorije.

Još jedno poboljšanje je uvođenje zajedničke države. Kada procesor upisuje u jednu od svojih linija lokalne predmemorije, obično generira signal za poništavanje kopija bloka koji se mijenja u drugim predmemorijama. U Berkeley protokolu, signal opoziva se generira samo ako druge predmemorije imaju takve kopije. To može značajno smanjiti nadzemni promet u autobusu. Mogući su sljedeći scenariji.

Prije svega, svaki put kada procesor upiše u svoju predmemoriju, promjenjivi niz se prenosi u "modificirano, privatno" (PD, Private Dirty) stanje. Nadalje, ako se red dijeli, na sabirnicu se šalje nevažeći signal, a u svim lokalnim predmemorijama gdje postoji kopija ovog bloka podataka, te se kopije prenose u "nevaljano" (I, Invalid) stanje. Ako dođe do promašaja pisanja, procesor dobiva kopiju bloka iz predmemorije trenutnog vlasnika traženog bloka. Tek nakon ovih radnji procesor upisuje u svoju predmemoriju.

U slučaju promašaja predmemorije čitanja, procesor šalje zahtjev vlasniku bloka da dobije najnoviju verziju potonjeg i prevodi njegovu novi primjerak u stanje samo za čitanje (RO, Read Only). Ako je redak bio u vlasništvu drugog procesora, on označava svoju kopiju bloka kao Dijeljeno prljavo (SD).

Dijagram stanja Berkeley protokola prikazan je na slici 1. 11.10.

Uspoređujući jednokratne protokole i Berkeley, može se primijetiti sljedeće. Oba protokola koriste strategiju povratnog upisivanja koja izmijenjene blokove drži u predmemoriji što je dulje moguće. Glavna memorija se ažurira samo kada se redak ukloni iz predmemorije. Gornja granica ukupnog broja transakcija pisanja na sabirnici određena je dijelom protokola za jednokratno upisivanje u kojem je implementirano pisanje, budući da potonja strategija generira operaciju pisanja na sabirnici sa svakom promjenom koju pokreće procesor. Budući da je prva operacija pisanja u protokolu pisanja s kraja na kraj, izvodi se čak i ako se podaci ne dijele. To podrazumijeva dodatni promet sabirnice, koja se povećava s povećanjem kapaciteta predmemorije. Dokazano je da protokol za jednokratno upisivanje rezultira većim prometom sabirnice od Berkeleyjevog protokola. .

|

Udarajte dok čitate

Riža. 11.10. Berkeley protokol

Redak protokola za jednokratno upisivanje koji se stalno čita i ažurira zahtijeva da se red pročita u predmemoriju, lokalno modificira u predmemoriji i zapiše natrag u memoriju. Cijeli postupak zahtijeva dvije operacije na sabirnici: čitanje iz glavne memorije (OP) i upisivanje natrag u OP. S druge strane, Berkeley protokol dolazi od preuzimanja vlasništva nad redom. Zatim se blok mijenja u predmemoriji. Ako se retku nije pristupilo prije nego što je uklonjen iz predmemorije, broj ciklusa sabirnice bit će isti kao u protokolu za jednokratno upisivanje. Međutim, vjerojatnije je da će red biti ponovno zatražen, tada s gledišta jedne cache memorije, ažuriranje reda predmemorije zahtijeva samo jednu operaciju čitanja na sabirnici. Dakle, Berkeley protokol prenosi linije izravno između predmemorije, dok protokol za jednokratno upisivanje prenosi blok iz izvorne predmemorije u glavnu memoriju, a zatim iz RAM-a u predmemoriju koja traži, što ima ukupnu latenciju memorijskog sustava. .

ProtokolIllinois. Protokol iz Illinoisa, koji je predložio Mark Papamarkos, također ima za cilj smanjiti promet autobusa, a time i vrijeme čekanja procesora na pristup autobusu. Ovdje, kao iu Berkeley protokolu, dominira ideja o vlasništvu nad blokovima, ali malo modificirana. U Illinois protokolu, svaka predmemorija koja ima valjanu kopiju bloka podataka ima vlasništvo. U tom slučaju, isti blok može imati više vlasnika. Kada se to dogodi, svakom procesoru se dodjeljuje određeni prioritet, a vlasnik s višim prioritetom postaje izvor informacija.

Kao iu prethodnom slučaju, signal za poništenje generira se samo kada postoje kopije ovog bloka u drugim predmemorijama. Mogući scenariji za Illinois protokol prikazani su na Sl. 11.11.

Riža. 11.11. Illinois protokol

Svaki put kada procesor upiše u svoju predmemoriju, promjenjivi red se stavlja u stanje PD (Private Dirty). Ako je podatkovni blok zajednički, signal za ukidanje šalje se na sabirnicu iu sve lokalne predmemorije, gdje postoji kopija ovog bloka, te se kopije prenose u "nevažeće" (I, Invalid) stanje. Ako dođe do promašaja pisanja, procesor dobiva kopiju iz predmemorije trenutnog vlasnika traženog bloka. Tek nakon ovih radnji, procesor upisuje u svoju predmemoriju. Kao što vidite, u ovom dijelu postoji potpuna podudarnost s Berkeley protokolom.

U slučaju promašaja predmemorije čitanja, procesor šalje zahtjev vlasniku bloka da dobije najnoviju verziju bloka i stavlja njegovu novu kopiju u "isključivo" (E, Exclusive) stanje, pod uvjetom da je jedini vlasnik reda. Inače, status se mijenja u "dijeljeno" (S, Shared).

Bitno je da je protokol proširiv i da je usko vezan i za stopu promašaja predmemorije i za količinu podataka koja je zajedničko svojstvo višeprocesorskog sustava.

Protokolkrijesnica. Protokol su predložili Tucker i suradnici i implementiran u Firefly Multiprocessor Workstation razvijenu u Istraživačkom centru Digital Equipment Corporation.

Protokol Firefly koristi zapis ažuriranja. Moguća stanja linije predmemorije ista su kao i kod protokola Illinois (Slika 11-12). Razlika je u tome što se politika povratnog upisivanja primjenjuje samo na retke u PD ili E stanju, dok se u retke u S stanju prepisuju. Predmemorije Observer koriste prepisivanje za ažuriranje svojih kopija. Osim toga, gledajte predmemorije koje pronađu kopiju linije u svom posjedu pokreću posebnu "dijeljenu" liniju sabirnice tako da kontroler pisanja može odlučiti u koje stanje staviti liniju u koju je napisana. “Zajednička” linija tijekom propusta čitanja predmemorije obavještava lokalni kontroler cache memorije o mjestu odakle je došla kopija retka: iz glavne memorije ili druge predmemorije. Dakle, stanje S primjenjuje se samo na podatke koji se stvarno dijele.

https://pandia.ru/text/78/264/images/image018_2.jpg" width="491 height=316" height="316">

Riža. 11.13. Zmajev protokol

ProtokolMESI. Svakako među poznatim protokolima samo promatranje je MESI (Modified/Exclusive/Shared/Invalid) protokol. MESI protokol se naširoko koristi u komercijalnim mikroprocesorskim sustavima, poput onih baziranih na Pentium i PowerPC mikroprocesorima. Dakle, može se naći u internoj predmemoriji i kontroleru vanjska predmemorija i82490 mikroprocesora Pentium, u procesoru i860 i keš kontroleru Motorola MC88200.

Protokol je dizajniran za predmemoriju s povratnim upisom. Jedan od glavnih ciljeva MESI protokola je što dulje odgoditi operaciju upisivanja predmemoriranih podataka u glavnu memoriju BC-a. To poboljšava performanse sustava minimizirajući potrebne prijenose informacija između predmemorije i glavne memorije. MESI protokol svakoj liniji predmemorije dodjeljuje jedno od četiri stanja, koja su kontrolirana s dva MESI statusna bita u oznaci retka. Status linije predmemorije može se promijeniti i procesor za koji je ova predmemorija lokalna i drugi procesori višeprocesorske sheme. Upravljanje stanjem linija predmemorije također se može dodijeliti vanjskim logičkim uređajima. Jedna verzija protokola predviđa korištenje prethodno razmatrane sheme za jednokratno upisivanje.

■podijeljeno(S, Shared) - redak u predmemoriji odgovara sličnoj liniji u glavnoj memoriji (podaci su valjani) i može biti prisutan u jednoj ili više drugih predmemorija.

■ Nevažeći(I, Nevažeći) - Redak predmemorije označen kao nevažeći ne sadrži valjane podatke i postaje logički nedostupan.

Riža. 11.15. Slijed promjena stanja u MESI protokolu: a - procesor 1 čita x;

b- procesor 2 čita x; c - procesor 1 čini prvi unos u x;

G- procesor 1 upisuje u x

Redoslijed kojim linija predmemorije prelazi iz jednog stanja u drugo ovisi o: trenutnom stanju retka, izvršenoj operaciji (čitanje ili pisanje), rezultatu pristupa predmemoriji (pogodan ili promašen) i konačno, hoće li redak dijeli se ili ne. Na sl. 11.14 prikazuje dijagram glavnih prijelaza bez uzimanja u obzir načina rada za jednokratno upisivanje.

Pretpostavimo da jedan od procesora uputi zahtjev za čitanje iz retka koji se trenutno ne nalazi u njegovoj lokalnoj predmemoriji (promašaj čitanja). Zahtjev će biti emitiran u autobusu. Ako nijedan od predmemorija ne pronađe kopiju željene linije, tada neće biti odgovora od nadzornih kontrolera drugih procesora, linija će se pročitati u predmemoriju procesora koji je tražio iz glavne memorije, a kopija će biti dodijeljena status E. Ako bilo koja od lokalnih predmemorija sadrži kopiju koja se traži, primit će se odgovor od odgovarajućeg nadzornika koji ukazuje na pristup dijeljenom nizu. Sve kopije dotičnog retka u svim predmemorijama bit će stavljene u stanje S, bez obzira u kojem su stanju prije bile (I, E ili S).

Kada procesor uputi zahtjev za pisanje na liniju koja nije u njegovoj lokalnoj predmemoriji (promašaj pisanja), linija se mora pročitati iz glavne memorije (MA) i izmijeniti prije nego što se učita u predmemoriju. Prije nego što procesor može učitati redak, mora se uvjeriti da zaista postoji valjana verzija podataka u glavnoj memoriji, odnosno da nema modificirane kopije danog retka u drugim predmemorijama. Slijed operacija formiran u ovom slučaju zove se čita s namjerom modifikatoracije(RWITM, čitanje s namjerom izmjene). Ako se kopija željene linije nađe u jednoj od predmemorija, štoviše, u stanju M, tada procesor koji ima tu kopiju prekida RWITM slijed i ponovno upisuje redak u OP, nakon čega mijenja stanje linije u njegova predmemorija u I. Zatim se RWITM slijed nastavlja i ponovno pristupa glavnoj memoriji kako bi se pročitao ažurirani redak. Konačno stanje retka bit će M, u kojem ni OP ni druge predmemorije nemaju drugu valjanu kopiju. Ako je kopija retka postojala u drugoj predmemoriji i nije imala stanje M, tada se takva kopija poništava i odmah se vrši pristup glavnoj memoriji.

Pogodak u predmemoriji prilikom čitanja ne mijenja status reda koji se čita. Ako procesor izvrši pristup pisanju postojećem redu koji je u stanju S, on odašilje zahtjev sabirnici da obavijesti druge predmemorije, ažurira red u svojoj predmemoriji i postavlja ga na status M. Sve ostale kopije retka su staviti u stanje I. Ako procesor izvrši pristup pisanju retku u stanju E, jedino što mora učiniti je upisati u red i promijeniti njegovo stanje u M, budući da u sustavu nema drugih kopija retka .

Na sl. Slika 11-15 prikazuje tipičan slijed događaja u dvoprocesorskom sustavu koji zahtijeva pristup lokaciji x. Pristup bilo kojoj ćeliji u retku predmemorije tretira se kao pristup cijeloj liniji.

Ilustrirajmo korake kada procesor 2 pokušava pročitati sadržaj ćelije x" (slika 11.16). Prvo dolazi do promašaja predmemorije čitanja i procesor pokušava pristupiti glavnoj memoriji. Procesor 1 prati sabirnicu, detektira poziv u ćeliju , čija se kopija nalazi u svojoj cache-memoriji i nalazi se u

|

Riža. 11.16. Prijelaz iz stanja E u stanje S u MESI protokolu: a - procesor 2

glasi x; b - procesor 1 proizvodi pisati natrag x" u glavnu memoriju;

i - procesor 2 čita x" iz glavne memorije

stanje M, tako da blokira operaciju čitanja iz procesora 2. Procesor 1 zatim prepisuje redak koji sadrži x" u OP i oslobađa procesor 2 kako bi mogao ponoviti pristup glavnoj memoriji. Procesor 2 sada prima redak koji sadrži x", i učitava ga u vašu predmemoriju. Oba primjerka su označena kao S.

Do sada smo razmatrali verziju MESI protokola bez jednog pisanja. S obzirom na pojedinačni unos, dijagram stanja prikazan na sl. 11.14, malo izmijenjeno. Svi promašaji predmemorije čitanja uzrokuju prijelaz u stanje S. Nakon prvog pogotka pisanja slijedi prijelaz u stanje E (tzv. prijelaz jednom zapisivanje). Sljedeći pogodak pisanja uzrokuje promjenu statusa retka u M.

Protokoli temeljeni na priručniku

Protokoli usklađenosti temeljeni na imeniku tipični su za složene višeprocesorske sustave sa zajedničkom memorijom, gdje su procesori ujedinjeni višestupanjskom hijerarhijskom mrežom međupovezivanja. Složenost topologije čini korištenje nadzornih protokola s njihovim mehanizmom emitiranja skupim i neučinkovitim.

Protokoli temeljeni na imeniku prikupljaju i prate informacije o sadržaju svih lokalnih predmemorija. Takvi se protokoli obično implementiraju pomoću centraliziranog kontrolera koji je fizički dio glavnog memorijskog kontrolera. Sam imenik je pohranjen u glavnoj memoriji. Kada lokalni kontroler predmemorije postavi zahtjev, kontroler imenika detektira takav zahtjev i generira naredbe potrebne za prijenos podataka iz glavne memorije ili iz druge lokalne predmemorije koja sadrži Najnovija verzija tražene podatke. Središnji kontroler odgovoran je za ažuriranje informacija o stanju lokalnih predmemorija, stoga mora biti obaviješten o svakoj lokalnoj radnji koja bi mogla utjecati na stanje podatkovnog bloka.

Direktorij sadrži skup unosa koji opisuju svaku predmemoriranu RT lokaciju koja se može dijeliti između procesora u sustavu. Imeniku se pristupa svaki put kada jedan od procesora modificira kopiju takve ćelije u svojoj lokalnoj memoriji. U ovom slučaju potrebne su informacije iz imenika kako bi se poništile ili ažurirale kopije promijenjene ćelije (ili cijelog retka koji sadrži ovu ćeliju) u drugim lokalnim predmemorijama gdje su takve kopije dostupne.

Za svaki zajednički redak koji se može predmemorirati, unos direktorija se dodjeljuje za pohranu pokazivača na kopije tog retka. Osim toga, u svakom unosu dodjeljuje se jedan modifikacijski bit (D), koji pokazuje je li kopija "prljava" (D = 1 - prljava) ili "čista" (D = 0 - čista), odnosno je li sadržaj redak u predmemoriji promijenio je memoriju nakon što je tamo učitan. Ovaj bit pokazuje smije li procesor pisati u zadani red.

Trenutačno postoje tri načina implementacije protokola koherencije predmemorije temeljenih na direktoriju: puni direktorij, ograničeni direktoriji i lančani direktoriji.

U protokolu potpuna referenca jedan centralizirani direktorij održava informacije o svim predmemorijama. Imenik je pohranjen u glavnoj memoriji.

|

Riža. 11.17. Full Reference Cache Coherence Protocol

U sustavu od N procesora, svaki unos imenika će sadržavati N pojedinačni bitni pokazivači. Ako je kopija podataka prisutna u odgovarajućoj lokalnoj predmemoriji, pokazivač bita je postavljen na 1, inače je postavljen na 0. 11.17. Ovo pretpostavlja da kopija niza postoji u svakoj predmemoriji. Svaki red ima dva indikatora statusa: valjani bit (V, Valid) i bit posjedovanja (P, Private). Ako su informacije u retku točne, njegov V-bit je postavljen na 1. Vrijednost P-bita od jedan označava da dati procesor dodijeljeno pravo upisivanja u odgovarajući redak svoje lokalne predmemorije.

Pretpostavimo da procesor 2 upisuje na mjesto x. U početnom trenutku procesor još nije dobio dopuštenje za takav zapis. Formira zahtjev kontroloru imenika i čeka dopuštenje za nastavak operacije. Kao odgovor na zahtjev za sve predmemorije u kojima postoje kopije retka koji sadrži ćeliju x, izdaje se signal za poništavanje postojećih kopija. Svaka predmemorija koja primi ovaj signal resetira nevažeći bit valjanosti reda (V-bit) na 0 i vraća signal potvrde kontroleru direktorija. Nakon primitka svih signala potvrde, kontroler imenika postavlja modifikacijski bit (D-bit) odgovarajućeg unosa imenika na jedan i šalje signal procesoru 2 kako bi omogućio upis na lokaciju x. Od ove točke nadalje, procesor 2 može nastaviti pisati u vlastitu kopiju lokacije x, kao iu glavnu memoriju ako se u predmemoriju implementira upisivanje.

Glavni problemi kompletnog referentnog protokola vezani su za veliki iznos zapisima. Za svaku ćeliju u imeniku sustava od N procesora potrebno je N+ 1 bitova, odnosno povećanjem broja procesora koeficijent složenosti raste linearno. Potpuni protokol direktorija omogućuje svakoj lokalnoj predmemoriji da ima kopije svih zajedničkih ćelija. U praksi ova mogućnost ne ostaje uvijek tražena - u svakom trenutku obično je relevantan samo jedan ili više primjeraka. U protokols ograničenim referencama kopije jednog retka mogu biti samo u ograničenom broju predmemorije - u isto vrijeme ne može biti više od P kopije niza, dok je broj pokazivača u unosima direktorija smanjen na n(n< N ). Za jedinstvenu identifikaciju cache memorije koja drži kopiju, pokazivač se mora sastojati od log2 N bita umjesto od jednog bita, a ukupna duljina pokazivača u svakom unosu direktorija treba umjesto toga N bitova bit će jednaka Plog2N malo. U konstantnoj vrijednosti P stopa rasta faktora složenosti ograničenog imenika kako se veličina sustava povećava niža je nego u slučaju linearnog odnosa.

Kad više od P kopija, kontrolor odlučuje koju će kopiju zadržati, a koju poništiti, nakon čega se vrše odgovarajuće promjene u pokazivačima za unos imenika.

Metoda povezani imenici također ima za cilj komprimiranje volumena imenika. Za pohranu zapisa koristi povezani popis koji se može implementirati kao jedan povezan (jednosmjerno) i dvostruko povezan (dvosmjerno).

Riža. 11.18. Protokol koherencije predmemorije povezanog imenika

U jednom povezanom popisu (slika 11.18), svaki unos u direktorij sadrži pokazivač na kopiju niza u jednoj od lokalnih predmemorija. Kopije istoimenih redaka u različite predmemorije sustavi čine jednosmjerni lanac. Da bi to učinili, njihove oznake imaju posebno polje u koje se upisuje pokazivač na cache memoriju koja sadrži sljedeću kopiju lanca. Poseban znak za razdvajanje stavlja se u oznaku posljednje kopije lanca. Ulančani imenik dopušta lance duljine N, odnosno podržava N kopije stanica. Prilikom stvaranja druge kopije, lanac se mora uništiti, a umjesto toga se mora formirati novi. Pretpostavimo, na primjer, procesor 5 nema kopiju ćelije x, a ona se za nju odnosi na glavnu memoriju. Pokazivač u direktoriju se mijenja tako da pokazuje na predmemoriju broj 5, a pokazivač u predmemoriji 5 se mijenja u pokazivač na predmemoriju 2. Da bi to učinio, glavni kontroler memorije mora proslijediti pokazivač predmemorije u predmemoriju 5 zajedno sa traženim podacima. -memorija broj 2. Tek nakon što se formira cijela struktura lanca, procesor 5 će dobiti dopuštenje za pristup ćeliji x. Ako procesor piše u ćeliju, tada se signal za ukidanje šalje stazom definiranom odgovarajućim lancem pokazivača. Lanac se također mora ažurirati kada se kopija ukloni iz bilo koje predmemorije.

Dvostruko povezani popis podržava pokazivače naprijed i natrag. To vam omogućuje učinkovitije umetanje novih pokazivača u lanac ili uklanjanje nepotrebnih iz njega, ali zahtijeva pohranjivanje većeg broja pokazivača.

Sheme koje se temelje na imeniku pate od "zagušenja" u centraliziranom kontroleru, kao i od komunikacijskih troškova na putovima između lokalnih kontrolera predmemorije i središnjeg kontrolera. Ipak, vrlo su učinkoviti u višeprocesorskim sustavima sa složenom topologijom međupovezivanja između procesora, gdje je nemoguće implementirati protokole za praćenje.

U nastavku je kratak opis trenutno relevantnih protokola za osiguranje koherentnosti predmemorije na temelju imenika. Za detaljnije upoznavanje s ovim protokolima daju se reference na relevantne književne izvore.

ProtokolTang. Postoji centralizirani globalni imenik koji sadrži cijeli primjerak sve informacije iz imenika svake od lokalnih predmemorija. To dovodi do problema uska grla, a također zahtijeva pronalaženje odgovarajućih ulaza.

Protokolcensier. Censierova shema imenika koristi vektor bita pokazivača da naznači koji procesori drže lokalnu kopiju danog bloka memorije. Takav vektor postoji za svaki memorijski blok. Nedostaci metode su njezina neučinkovitost s velikim brojem procesora, a osim toga potreban je pristup glavnoj memoriji za ažuriranje linija predmemorije.

ProtokolArchibald. Schema Archibaldovog priručnika je par složenih shema za hijerarhijski organizirane mreže procesora. IZ Detaljan opis ovaj protokol se može naći u .

ProtokolStenstrom. Stenstrom vodič pruža šest valjanih stanja za svaki podatkovni blok. Ovaj protokol je relativno jednostavan i prikladan je za bilo koju topologiju međupovezivanja procesora. Imenik je pohranjen u glavnoj memoriji. U slučaju propusta predmemorije za čitanje pristupa se glavnoj memoriji koja šalje poruku u predmemoriju vlasnika bloka, ako postoji. Nakon primitka ove poruke, vlasnik predmemorije šalje tražene podatke i također šalje poruku svim ostalim procesorima koji dijele podatke da ažuriraju svoje bitvektore. Shema nije vrlo učinkovita s velikim brojem procesora, međutim, trenutno je najrazvijeniji i najrašireniji protokol priručnika.

Kontrolirati pitanja

1. Analizirajte utjecaj dijeljene memorije i značajke distribuirane memorije VS na razvoj softvera. Zašto se ovi VS nazivaju jako spregnuti, odnosno slabo povezani?

2. Objasnite ideju izmjeničnih memorijskih adresa. Koja su razmatranja pri odabiru mehanizma za dodjelu adresa? Kako je to povezano s klasom arhitekture zrakoplova?

3. Dajte komparativna karakteristika homogeni i heterogeni pristupi

na sjećanje.

4. Koje su prednosti SOMA arhitekture?

5. Provesti komparativnu analizu modela s cache-koherentnim i cache-inkoherentnim pristupom heterogenoj memoriji.

6. Formulirajte prednosti i nedostatke arhitekture bez izravnog pristupa udaljenoj memoriji.

7. Objasnite značenje distribuirane i zajedničke memorije.

8. Razvijte vlastiti primjer kako biste ilustrirali problem koherentnosti predmemorije.

9. Opišite značajke softverski načini rješenja problema koherentnosti, istaknuti njihove prednosti i nedostatke.

10. Usporedite metode zapisivanja u pamćenje s poništavanjem i zapisivanja u pamćenje s prijevodom, naglašavajući njihove prednosti i nedostatke.

11. Dajte usporedni opis metoda za održavanje koherencije u višeprocesorskim sustavima.

12. Izvršite komparativnu analizu vama poznatih protokola promatranja.

13. Koji je najpopularniji nadzorni protokol? Obrazložite razloge povećanog interesa za njega.

14. Dajte detaljan opis koherentnih protokola na temelju priručnika i kako ih implementirati. Koja je razlika između ovih protokola i protokola promatranja?

| № | Vrsta memorije | 1985 | 2000 | ||||

|---|---|---|---|---|---|---|---|

| Vrijeme uzorka | Tipični volumen | Cijena / bajt | Vrijeme uzorka | Tipični volumen | Cijena / bajt | ||

| 1 | Super-brza memorija (registri) | 0,2 5 ns | 16/32 bit | $ 3 - 100 | 0,01 1 ns | 32/64/128 bit | $ 0,1 10 |

| 2 | Brza memorija međuspremnika (cache) | 20 100 ns | 8Kb - 64Kb | ~ $ 10 | 0,5 - 2 ns | 32Kb 1Mb | $ 0,1 - 0,5 |

| 3 | Operativna (glavna) memorija | ~ 0,5 ms | 1Mb - 256Mb | $ 0,02 1 | 2 ns 20 ns | 128 MB - 4 GB | $ 0,01 0,1 |

| 4 | Vanjska pohrana (masovna pohrana) | 10 - 100 ms | 1Mb - 1Gb | $ 0,002 - 0,04 | 5 - 20 ms | 1GB - 0,5TB | $ 0,001 - 0,01 |

Registri procesora čine njegov kontekst i pohranjuju podatke koje koriste procesorske instrukcije koje trenutno izvršavaju. Registri procesora se u pravilu nazivaju svojim mnemoničkim oznakama u naredbama procesora.

Cache koristi se za usklađivanje brzine CPU-a i glavne memorije. U računalnim sustavima koristi se predmemorija na više razina: predmemorija razine I (L1), predmemorija razine II (L2) itd. Stolni sustavi obično koriste predmemoriju na dvije razine, dok poslužitelji koriste predmemoriju na tri razine. Predmemorija pohranjuje upute ili podatke koje će procesor vjerojatno obraditi u bliskoj budućnosti. Rad cache memorije je transparentan za softver, dakle cache memorija obično nisu programski dostupni.

radna memorija trgovine, u pravilu, funkcionalno dovršene softverski moduli(jezgra operacijskog sustava, izvršni programi i njihove knjižnice, upravljački programi korištenih uređaja itd.) i njihovi podaci koji su izravno uključeni u rad programa, a također se koriste za spremanje rezultata izračuna ili druge obrade podataka prije prijenosa na vanjski memoriju, na izlaz podataka uređaja ili komunikacijska sučelja.

Svaka ćelija RAM memorija dodijeljena jedinstvena adresa. Organizacijske metode dodjele memorije omogućuju programerima mogućnost učinkovitog korištenja cijele računalni sustav. Te metode uključuju čvrsti ("ravni") model memorije i model segmentirane memorije. Korištenje solidan model( flat model ) memorije, program radi s jednim kontinuiranim adresnim prostorom, linearnim adresnim prostorom u kojem se memorijske ćelije numeriraju uzastopno i kontinuirano od 0 do 2n-1, gdje je n dubina bita CPU-a na adresi. Kada se za program koristi segmentirani model, memorija je predstavljena grupom neovisnih adresnih blokova koji se nazivaju segmenti. Za adresiranje memorijskog bajta, program mora koristiti logičku adresu, koja se sastoji od selektora segmenta i pomaka. Selektor segmenata odabire određeni segment, a pomak pokazuje na određenu ćeliju u adresnom prostoru odabranog segmenta.