Capitolo 11

Organizzazione calcolo della memoria sistemi

Nei sistemi informatici che combinano molti processori o macchine parallele, il compito organizzazione corretta la memoria è una delle più importanti. La differenza tra velocità del processore e della memoria è sempre stata un ostacolo nelle VM uniprocessore. Il multiprocessing VS porta a un altro problema: il problema dell'accesso simultaneo alla memoria da più processori.

A seconda di come è organizzata la memoria dei sistemi multiprocessore (multicomputer), i sistemi informatici si distinguono con memoria condivisa(memoria condivisa) e VS con memoria distribuita. V sistemi di memoria condivisa(spesso è chiamata anche memoria condivisa o condivisa) La memoria del Sole è considerata una risorsa comunitaria, e ciascuno dei processori ha accesso completo all'intero spazio degli indirizzi. I sistemi di memoria condivisa sono chiamati legato strettamente(sistemi strettamente accoppiati). Una costruzione simile di sistemi di calcolo avviene sia nella classe SIMD che nella classe MIMD. A volte, per sottolineare questa circostanza, vengono introdotte sottoclassi speciali, usando le abbreviazioni SM-SIMD (Shared Memory SIMD) e SM-MIMD (Shared Memory MIMD) per denotarle.

In opzione con memoria distribuita a ciascuno dei processori è assegnata la propria memoria. I processori si fondono v rete e possono, all'occorrenza, scambiare i dati conservati nella loro memoria, trasmettendosi reciprocamente le cosiddette messaggi. Questo tipo di aereo si chiama debolmente accoppiato(sistemi debolmente accoppiati). Debolmente sistemi correlati si trovano anche sia nella classe SIMD che nella classe MIMD, e talvolta per enfatizzare questa caratteristica, introdurre le sottoclassi DM-SIMD (Distributed Memory SIMD) e DM-MIMD (Distributed Memory MIMD).

In alcuni casi vengono chiamati sistemi informatici con memoria condivisa multiprocessore, e sistemi con memoria distribuita - mtsltcomputer.

La differenza tra la memoria condivisa e quella distribuita è la differenza nella struttura memoria virtuale, ovvero nell'aspetto della memoria dal lato del processore. Fisicamente, quasi tutti i sistemi di memoria sono suddivisi in componenti indipendenti cui si accede in modo autonomo. Il modo in cui il sottosistema di memoria interpreta l'indirizzo di cella ricevuto dal processore è scollegato dalla memoria condivisa. Ad esempio, supponiamo che il processore esegua il comando load RO, i, che significa "Load register R0 con il contenuto della cella i". Nel caso della memoria condivisa, i è l'indirizzo globale e punta alla stessa posizione per qualsiasi processore. V sistema distribuito ricordo che sono indirizzo locale Se due processori eseguono il comando load RO, i, allora ognuno di loro accede i-esima cella nella sua memoria locale, cioè to cellule diverse e valori disuguali possono essere caricati nei registri R0.

La differenza tra i due sistemi di memoria deve essere tenuta presente dal programmatore, in quanto determina il modo in cui interagiscono parti di un programma parallelo. Nella variante con memoria condivisa è sufficiente creare una struttura dati in memoria e trasferire i riferimenti a tale struttura a sottoprogrammi paralleli. In un sistema a memoria distribuita, è necessario disporre di una copia dei dati condivisi in ciascuna memoria locale. Queste copie vengono create annidando i dati condivisi nei messaggi inviati ad altri processori.

Memoria Con alternato indirizzi

Fisicamente, la memoria di un sistema informatico è costituita da più moduli (banchi), mentre la questione essenziale è come viene distribuito lo spazio degli indirizzi in questo caso (l'insieme di tutti gli indirizzi che il processore può formare). Un modo per distribuire indirizzi virtuali tra i moduli di memoria consiste nel suddividere lo spazio degli indirizzi in blocchi sequenziali. Se la memoria è composta da P banche, quindi la cella con l'indirizzo io in caso di frazionamento in blocco, sarà in banca con il numero io /n. Nel sistema memoria interlacciata(memoria interlacciata) gli indirizzi consecutivi si trovano in banchi diversi: la cella con indirizzo i è nel banco con numero i mod P. Poniamo, per esempio, che la memoria sia composta da quattro banchi da 256 byte ciascuno. In uno schema di indirizzamento a blocchi, verrà allocato il primo banco indirizzi virtuali 0-255, il secondo - 256-511, ecc. In uno schema con indirizzi alternati, le celle consecutive nel primo banco avranno indirizzi virtuali 0, 4, 8, .... nel secondo banco - 1, 5, 9 , ecc. (Figura 11.1, a).

La distribuzione dello spazio indirizzi tra i moduli permette di elaborare contemporaneamente richieste di accesso alla memoria, se i corrispondenti indirizzi appartengono a banchi diversi, il processore può richiedere l'accesso ad una cella in uno dei cicli io e nel ciclo successivo - alla cella j. Se Io eJ si trovano in banchi diversi, le informazioni verranno trasmesse in cicli successivi. Qui, un ciclo si riferisce a un ciclo del processore, mentre un ciclo di memoria completo richiede diversi cicli del processore. Pertanto, in questo caso, il processore non deve attendere il completamento dell'intero ciclo di accesso alla cella. io. La tecnica considerata consente di aumentare il throughput: se il sistema di memoria è composto da

https://pandia.ru/text/78/264/images/image002_61.jpg "width =" 62 "height =" 15 "> Viene chiamata la spaziatura tra gli elementi passo per indice o Passo(passo). Uno di applicazioni interessanti questa proprietà può fungere da Accesso alle matrici. Se il passo indice è uno in più rispetto al numero di righe della matrice, una singola richiesta di accesso alla memoria restituirà tutti gli elementi diagonali della matrice (Figura 11.1, b). La responsabilità di garantire che tutti gli elementi recuperati della matrice si trovino in banchi diversi spetta al programmatore.

Modelli di architettura di memoria dei sistemi informatici

Sia all'interno della memoria condivisa che di quella distribuita, sono implementati diversi modelli di architetture di sistemi di memoria.

DIV_ADBLOCK84 ">

Riso. 11.3. Memoria condivisa: a - combinazione di processori mediante bus; b - un sistema con cache locali; v- prestazioni del sistema in funzione del numero di processori sul bus; d - VS multiprocessore con memoria condivisa, costituito da moduli separati

Modo alternativo la costruzione di un VS multiprocessore con memoria condivisa basata su NML è mostrata in Fig. 11.3, G. Qui il picco viene sostituito da uno switch che indirizza le richieste del processore a uno dei numerosi moduli di memoria. Nonostante il fatto che ci siano diversi moduli di memoria, appartengono tutti a un singolo spazio di indirizzi virtuali. Il vantaggio di questo approccio è che lo switch è in grado di servire più richieste in parallelo. Ogni processore può essere collegato al proprio modulo di memoria e accedervi alla massima velocità consentita. Quando si tenta di accedere allo stesso modulo di memoria contemporaneamente, può sorgere rivalità tra i processori. In questo caso, solo un processore ottiene l'accesso e gli altri vengono bloccati.

Sfortunatamente, l'architettura UMA non si adatta bene. I sistemi più comuni contengono 4-8 processori, molto meno spesso 32-64 processori. Inoltre, tali sistemi non possono essere classificati come tolleranti ai guasti, poiché il guasto di un processore o di un modulo di memoria comporta il guasto dell'intero aeromobile.

Un altro approccio alla costruzione di una memoria condivisa VS è accesso non uniforme alla memoria, indicato come NUM A (Accesso alla memoria non uniforme), c'è ancora un singolo spazio di indirizzi, ma ogni processore ha memoria locale. Il processore accede direttamente alla propria memoria locale, che è molto più veloce dell'accesso alla memoria remota tramite uno switch o una rete. Un tale sistema può essere integrato con la memoria globale, quindi i dispositivi di archiviazione locali fungono da memoria cache veloce per la memoria globale. Tale schema può migliorare le prestazioni dell'aeromobile, ma non è in grado di ritardare indefinitamente l'equalizzazione della prestazione diretta. Se ogni processore ha una cache locale (Figura 11.3.6), c'è un'alta probabilità (p> 0.9) che il comando oi dati richiesti siano già presenti nella memoria locale. La ragionevole probabilità di colpire la memoria locale riduce significativamente il numero di chiamate al processore a memoria globale e quindi porta ad una maggiore efficienza. Il luogo della rottura nella curva delle prestazioni (la curva superiore in Fig.11.3, v), il punto in cui l'aggiunta di processori è ancora effettiva viene ora spostato nella regione del processore 20 e il più sottile, dove la curva diventa orizzontale, nella regione del processore 30.

All'interno del concetto NUMA sono implementati diversi approcci, indicati con abbreviazioni SOMA,CC-NUMA e NCC-NUMA.

V architettura di sola cache(SOMA, Cache Only Memory Architecture) La memoria locale di ciascun processore è costruita come una grande cache per accesso veloce dal lato del "proprio" processore. Le cache di tutti i processori sono considerate collettivamente la memoria globale del sistema. Non esiste una memoria globale effettiva. La caratteristica fondamentale del concetto SOMA si esprime nella dinamica. Qui, i dati non sono staticamente legati a un modulo di memoria specifico e non hanno un indirizzo univoco che rimane invariato per l'intera durata della variabile. Nell'architettura SOMA i dati vengono trasferiti alla memoria cache dell'ultimo processore che li ha richiesti, mentre la variabile non è fissata con un indirizzo univoco e può essere localizzata in qualsiasi cella fisica in qualsiasi momento. Lo spostamento dei dati da una cache locale a un'altra non richiede la partecipazione a questo processo sistema operativo ma implica hardware di gestione della memoria complesso e costoso. Per organizzare un tale regime, il cosiddetto directory della cache. Nota anche che l'ultima copia dell'elemento non viene mai rimossa dalla cache.

Poiché nell'architettura SOMA i dati vengono spostati nella memoria cache locale del processore proprietario, tali velivoli hanno un significativo vantaggio prestazionale rispetto ad altre architetture NUM A. D'altra parte, se una singola variabile o due variabili diverse memorizzano la stessa cache in una è richiesta da due processori, questa linea di cache deve essere spostata avanti e indietro tra i processori ogni volta che si accede ai dati. Tali effetti possono dipendere dai dettagli dell'allocazione della memoria e portare a situazioni imprevedibili.

Modello accesso alla memoria non uniforme coerente con la cache(CC-NUMA, Сache Coherent Non-Uniform Memory Architecture) è fondamentalmente diverso dal modello SOMA. Il sistema CC-NUMA non utilizza la memoria cache, ma la solita memoria allocata fisicamente. Non avviene alcuna copia di pagine o dati tra le locazioni di memoria. Non ci sono messaggi software. C'è solo una memory stick, con parti fisicamente collegate tramite cavo di rame e hardware intelligente. La coerenza della cache basata sull'hardware significa che non è necessario alcun software per archiviare più copie di dati aggiornati o trasferirli. Il livello hardware gestisce tutto questo. L'accesso ai moduli di memoria locale in diversi nodi del sistema può essere eseguito contemporaneamente ed è più veloce rispetto ai moduli di memoria remoti.

La differenza tra il modello con accesso alla memoria non uniforme incoerente nella cache(NCC-NUMA, Non-Cache Coherent Non-Uniform Memory Architecture) di CC-NUMA è ovvio dal nome. L'architettura della memoria presuppone un singolo spazio di indirizzi, ma non fornisce la consistenza hardware dei dati globali. La gestione dell'utilizzo di tali dati spetta interamente al software (applicazioni o compilatori). Nonostante questa circostanza, che sembra essere uno svantaggio dell'architettura, risulta essere molto utile nell'incrementare le prestazioni dei sistemi informatici con un'architettura di memoria di tipo DSM, considerata nella sezione "Modelli di architetture di memoria distribuita".

In generale si chiamano AC con memoria condivisa costruiti secondo lo schema NUMA architetture di memoria virtuale condivisa(architetture di memoria virtuale condivisa). Questo tipo architettura, in particolare CC-NUMA, in Di recenteè considerato un tipo indipendente e piuttosto promettente di sistemi informatici della classe MIMD, pertanto tale velivolo sarà discusso in maggior dettaglio di seguito.

Modelli di architettura di memoria distribuita

In un sistema a memoria distribuita, ogni processore ha la propria memoria e può solo indirizzarla. Alcuni autori chiamano questo tipo di sistemi aereo multicomputer o multicomputer, evidenziando il fatto che gli elementi costitutivi di un sistema sono essi stessi piccoli sistemi informatici con un processore e una memoria. I modelli di architetture di memoria distribuita sono generalmente indicati come architettura senza accesso diretto alla memoria remota(NORMA, nessun accesso alla memoria remota). Questo nome deriva dal fatto che ogni processore ha accesso solo alla sua memoria locale. L'accesso alla memoria remota (memoria locale di un altro processore) è possibile solo scambiando messaggi con il processore proprietario della memoria indirizzabile.

Questa organizzazione ha una serie di vantaggi. Innanzitutto, quando si accede ai dati, non c'è concorrenza per il bus o gli switch: ogni processore può utilizzare completamente la larghezza di banda del percorso di comunicazione con la propria memoria locale. In secondo luogo, l'assenza di un bus condiviso significa che non ci sono restrizioni associate al numero di processori: la dimensione del sistema è limitata solo dalla rete di processori. Terzo, il problema della coerenza della cache viene rimosso. Ciascun processore ha il diritto di modificare in modo indipendente i propri Dati senza preoccuparsi di far corrispondere le copie dei dati nella propria memoria cache locale con le cache di altri processori.

Il principale svantaggio di un computer a memoria distribuita è la complessità dello scambio di informazioni tra processori. Se uno dei processori necessita di dati dalla memoria di un altro processore, deve scambiare messaggi con questo processore. Ciò comporta due tipi di costi:

· Ci vuole tempo per formare e inoltrare un messaggio da uno! processore a un altro;

· Per fornire una risposta ai messaggi provenienti da altri processori, il processore ricevente deve ricevere una richiesta di interruzione ed eseguire la procedura per la gestione di tale interruzione.

La struttura di un sistema di memoria distribuita è mostrata in Fig. 11.4. Sulla sinistra! parti (fig.11.4, un) viene mostrato un elemento di elaborazione (PE). Comprende) il processore stesso (P), la memoria locale (M) e due controller I/O (Ko e KD Sul lato destro (Fig.11.4, B) viene mostrato un sistema a quattro processori che illustra come i messaggi vengono inviati da un processore all'altro. In relazione a ciascun PE, tutti gli altri elementi di elaborazione possono essere visti semplicemente come dispositivi di input/output. Per inviare un messaggio ad un altro PE, il processore forma un blocco di dati nella sua memoria locale e notifica il suo controller locale sulla necessità di trasferire informazioni su un dispositivo esterno. Attraverso la rete di interconnessione, questo messaggio viene inoltrato al controller I/O ricevente del PE ricevente. Quest'ultimo trova spazio per il messaggio nella propria memoria locale e notifica al processore sorgente che il messaggio è stato ricevuto.

DIV_ADBLOCK89 ">

Una variante interessante di un sistema di memoria distribuita è; modello memoria condivisa distribuita(DSM, Distribute Shared Memory), noto anche con un altro nome architettura con eterogeneitàaccesso alla memoria e coerenza del software(SC-NUMA, architettura di memoria non uniforme coerente con il software). L'idea di questo modello è che il BC, essendo fisicamente un sistema con memoria distribuita, grazie al sistema operativo appaia all'utente come un sistema con memoria condivisa. Ciò significa che il sistema operativo offre all'utente un unico spazio di indirizzamento, nonostante l'effettivo accesso alla memoria del computer dell'aereo "straniero" sia ancora fornito attraverso lo scambio di messaggi.

Multiprocessorecoerenza cache- memoria

Un sistema multiprocessore a memoria condivisa è costituito da due o più processori indipendenti, ciascuno dei quali esegue una parte di un programma di grandi dimensioni o un programma indipendente. Tutti i processori accedono alle istruzioni e ai dati archiviati nella memoria principale condivisa. Poiché la memoria è una risorsa condivisa, c'è concorrenza tra i processori quando vi si accede, il che aumenta la latenza media di accesso alla memoria. Per ridurre questa latenza, a ciascun processore viene assegnata una cache locale che, servendo gli accessi alla memoria locale, in molti casi evita la necessità di accedere alla memoria principale condivisa. A sua volta, dotare ogni processore di una memoria cache locale porta al cosiddetto problema di coerenza o fornendo in accordomemoria cache. Secondo il sistema, il sistema è coerente se ogni operazione di lettura a un certo indirizzo, eseguita da uno qualsiasi dei processori, restituisce il valore immesso durante l'ultima operazione di scrittura a questo indirizzo, indipendentemente da quale processore è stato l'ultimo a scrivere.

V la forma più semplice il problema della coerenza della cache può essere spiegato come segue (Figura 11.5). Lascia che due processori Rg e Pr sono collegati alla memoria condivisa tramite bus. Innanzitutto, entrambi i processori leggono la variabile X. Le copie dei blocchi contenenti questa variabile vengono trasferite dalla memoria principale alle cache locali di entrambi i processori (Figura 11.5, un). Quindi il processore Pt esegue l'operazione di incremento del valore della variabile X per unità. Poiché una copia della variabile è già presente nella cache di questo processore, si verificherà un accesso alla cache e il valore verrà modificato solo nella cache 1. Se ora il processore P2 esegue nuovamente un'operazione di lettura X, quindi si verificherà anche un colpo alla cache e P2 riceverà il "vecchio" valore memorizzato nella sua memoria cache X(fig.11.5, B).

Il mantenimento della coerenza richiede che quando un dato viene modificato da uno dei processori, le modifiche corrispondenti vengano apportate nella memoria cache degli altri processori, dove è presente una copia del dato modificato, nonché nella memoria condivisa. Un problema simile si verifica, tra l'altro, nei sistemi uniprocessore, dove ci sono diversi livelli di memoria cache. Qui è necessario riconciliare il contenuto di cache di diversi livelli.

Esistono due approcci per risolvere il problema della coerenza: software e hardware. Alcuni sistemi utilizzano strategie che combinano entrambi gli approcci.

Software modi soluzioniI problemi coerenza

Le tecniche software per risolvere il problema della coerenza consentono di farne a meno equipaggiamento aggiuntivo o ridurlo al minimo.

ProtocolloBerkeley. Il protocollo Berkeley è stato utilizzato nel sistema multiprocessore Berkeley basato su processori RISC.

Il sovraccarico di cache miss è mitigato dall'idea del protocollo di proprietà di una linea di cache. Generalmente, la memoria principale è considerata la proprietaria di tutti i blocchi di dati. Prima di modificare il contenuto di una riga nella sua cache, il processore deve acquisire la proprietà della riga. Tali diritti vengono acquisiti tramite speciali operazioni di lettura e scrittura. Se, accedendo ad un blocco, il cui titolare in questo momento non è la memoria principale, si verifica un errore di cache, il processore proprietario della riga impedisce la lettura dalla memoria principale e alimenta il processore richiedente con i dati dalla sua stessa cache locale.

Un altro miglioramento è l'introduzione di uno stato condiviso. Quando il processore scrive su una delle righe della sua memoria cache locale, di solito genera un segnale per scartare copie del blocco modificabile in altre cache. Nel protocollo Berkeley, il segnale di scarto viene generato solo se sono presenti tali copie in altre cache. Ciò può ridurre significativamente il traffico di autobus improduttivo. Sono possibili i seguenti scenari.

Prima di tutto, ogni volta che un processore scrive nella sua memoria cache, la stringa mutabile viene messa in uno stato Private Dirty (PD). Inoltre, se la stringa è condivisa, viene inviato un segnale di invalidazione al bus e in tutte le cache locali in cui è presente una copia di questo blocco di dati, tali copie vengono poste nello stato "non valido" (I, Invalid). In caso di write miss, il processore ottiene una copia del blocco dalla cache del master corrente del blocco richiesto. Solo dopo queste azioni il processore scrive nella sua cache.

In caso di read cache miss, il processore invia una richiesta al proprietario del blocco per ottenere la versione più recente di quest'ultimo, e mette la sua nuova copia nello stato di "sola lettura" (RO, Read Only). Se la riga era di proprietà di un altro processore, contrassegna la sua copia del blocco come Shared Dirty (SD).

Il diagramma di stato del protocollo Berkeley è mostrato in Fig. 11.10.

Confrontando i protocolli write-once e Berkeley, si può notare quanto segue. Entrambi i protocolli utilizzano la strategia rispondere, in cui i blocchi modificati vengono conservati nella memoria cache il più a lungo possibile. La memoria principale viene aggiornata solo quando una riga viene eliminata dalla cache. Il limite superiore al numero totale di transazioni di scrittura sul bus è determinato da quella parte del protocollo write-once che implementa il write-through, poiché quest'ultima strategia genera un'operazione di scrittura sul bus ad ogni modifica avviata dal processore. Poiché la prima operazione di scrittura in un protocollo write-once è pass-through, viene eseguita anche se i dati non sono condivisi. Questo comporta traffico aggiuntivo bus, che aumenta con l'aumentare della capacità della cache. È stato dimostrato che il protocollo write-once genera più traffico bus rispetto al protocollo Berkeley .

|

Colpo di lettura

Riso. 11.10. Protocollo Berkeley

Una riga leggibile e aggiornata nel protocollo write-once richiede che la riga venga letta nella cache, modificata localmente nella cache e riscritta in memoria. L'intera procedura richiede due operazioni sul bus: la lettura dalla memoria principale (RAM) e la riscrittura nella RAM. Il protocollo Berkeley, d'altra parte, riguarda l'acquisizione dei permessi di riga. Quindi il blocco viene modificato nella cache. Se non è stato effettuato l'accesso alla riga prima della cancellazione dalla cache, i cicli del bus saranno gli stessi del protocollo write-once. Tuttavia, è più probabile che la linea venga richiesta nuovamente, quindi dal punto di vista di una singola memoria cache, l'aggiornamento della linea cache richiede una sola operazione di lettura sul bus. Pertanto, il protocollo Berkeley trasferisce le linee direttamente tra le cache, mentre il protocollo write-once trasferisce un blocco dalla cache originale alla memoria principale e quindi dall'OP alle cache richiedenti, determinando una latenza complessiva del sistema di memoria. .

ProtocolloIllinois. Il protocollo Illinois, proposto da Marc Papamarcos, mira anche a ridurre il traffico bus e quindi il timeout del processore per l'accesso al bus. Qui, come nel protocollo di Berkeley, l'idea della proprietà dei blocchi è dominante, ma leggermente modificata. Nel protocollo dell'Illinois, la proprietà è detenuta da qualsiasi cache che contenga una copia valida di un blocco di dati. In questo caso, lo stesso blocco può avere più proprietari. Quando ciò accade, a ciascun processore viene assegnata una certa priorità e il proprietario con una priorità più alta diventa la fonte delle informazioni.

Come nel caso precedente, il segnale di invalidazione viene generato solo quando copie di questo blocco sono disponibili in altre cache. Scenari possibili per il protocollo Illinois sono mostrati in Fig. 11.11.

Riso. 11.11. Protocollo dell'Illinois

Ogni volta che un processore scrive nella sua cache, la stringa modificata viene posta in uno stato Private Dirty (PD).Se il blocco di dati è condiviso, viene inviato un segnale di kill al bus e in tutte le cache locali è presente una copia di questo blocco , queste copie vengono trasferite allo stato "non valido" (I, Non valido). Se si verifica un errore di scrittura, il processore recupera una copia dalla cache dell'attuale proprietario del blocco richiesto. Solo dopo le azioni indicate, il processore scrive nella sua cache. Come puoi vedere, in questa parte c'è una coincidenza completa con il protocollo di Berkeley.

In caso di read cache miss, il processore invia una richiesta al proprietario del blocco per ottenere la versione più recente di quest'ultimo, e pone la sua nuova copia nello stato "exclusive" (E, Exclusive), purché sia l'unico proprietario della riga. In caso contrario, lo stato viene modificato in "condiviso" (S, Condiviso).

È essenziale che il protocollo sia estensibile e strettamente legato sia al rapporto di missaggio della cache sia alla quantità di dati che è proprietà comune di un sistema multiprocessore.

ProtocolloLucciola. Il protocollo è stato proposto da Tucker et al e implementato nella Firefly Multiprocessor Workstation, un sistema multiprocessore sviluppato presso il centro di ricerca della Digital Equipment Corporation.

Il protocollo Firefly utilizza un record di aggiornamento. I possibili stati della linea della cache sono gli stessi del protocollo Illinois (Figura 11-12). La differenza è che la strategia di writeback si applica solo alle righe nello stato PD o E, mentre il write-through si applica alle righe nello stato S. Le cache Watcher utilizzano la scrittura tramite scrittura per aggiornare le proprie copie. Inoltre, osservando le cache che trovano in esse una copia della linea, si richiama una speciale linea di bus "condivisa" in modo che il controller di scrittura possa decidere in quale stato mettere la linea in cui è stata scritta. Una riga "condivisa" su un miss cache di lettura serve per informare il controller della cache locale da dove proviene la copia della riga: dalla memoria principale o da un'altra cache. Pertanto, lo stato S si applica solo ai dati che vengono effettivamente condivisi.

https://pandia.ru/text/78/264/images/image018_2.jpg "larghezza =" 491 altezza = 316 "altezza =" 316 ">

Riso. 11.13. Protocollo del drago

ProtocolloMESI. Naturalmente, tra i protocolli di sorveglianza più conosciuti, il più diffuso è il protocollo MESI (Modificato/Esclusivo/Condiviso/Non valido). Il protocollo MESI è ampiamente utilizzato in ambito commerciale sistemi a microprocessore, ad esempio basati su microprocessori Pentium e PowerPC. Quindi, può essere trovato nella cache interna e nel controller cache esterna i82490 del microprocessore Pentium, nel processore i860 e nel controller cache MC88200 di Motorola.

Il protocollo è stato progettato per le cache write-back. Uno degli obiettivi principali del protocollo MESI è quello di rimandare il più a lungo possibile il writeback dei dati incapsulati nella memoria principale BC. Ciò migliora le prestazioni del sistema riducendo al minimo i necessari trasferimenti di informazioni tra le cache e la memoria principale. Il protocollo MESI assegna a ciascuna linea della cache uno dei quattro stati, che sono controllati dai due bit di stato MESI nel tag di quella linea. Lo stato della linea cache può essere modificato sia dal processore, per il quale questa memoria cache è locale, sia da altri processori dello schema multiprocessore ". La gestione dello stato delle linee cache può essere affidata a dispositivi logici esterni. Una delle versioni del protocollo prevede l'utilizzo dello schema write-once precedentemente considerato.

■Condivisa(S, Shared) - una linea di cache corrisponde a una linea simile nella memoria principale (i dati sono validi) e può essere presente in una o più delle altre cache.

■ Non valido(I, Invalid) - Una riga della cache contrassegnata come non valida non contiene dati validi e diventa logicamente inaccessibile.

Riso. 11.15. La sequenza dei cambiamenti di stato nel protocollo MESI: a - il processore 1 legge x;

B- il processore 2 legge x; c - il processore 1 effettua il primo record in x;

G- il processore 1 fa un altro record in x

L'ordine in cui una linea di cache passa da uno stato all'altro dipende da: lo stato corrente della linea, l'operazione in corso (lettura o scrittura), il risultato dell'accesso alla cache (hit or miss) e, infine, se la linea è condivisa o meno. Nella fig. 11.14 mostra un diagramma delle principali transizioni senza tener conto della modalità write-once.

Supponiamo che uno dei processori effettui una richiesta di lettura da una linea che non è attualmente nella sua cache locale (read miss). La richiesta sarà trasmessa sul bus. Se nessuna delle cache contiene una copia della riga richiesta, non ci sarà risposta dai controller di monitoraggio di altri processori, la linea verrà letta nella cache del processore richiedente dalla memoria principale e la copia verrà assegnata lo stato E. Se una qualsiasi delle cache locali contiene la copia che stai cercando, verrà ricevuta una risposta dal controller tracker corrispondente che indica l'accesso alla stringa condivisa. Tutte le copie della riga in questione in tutte le cache verranno trasferite allo stato S, indipendentemente dallo stato in cui si trovavano prima (I, E o S).

Quando un processore effettua una richiesta di scrittura su una stringa che non si trova nella sua cache locale (write miss), la stringa deve essere letta dalla memoria principale (RAM) e aggiornata prima di essere caricata nella memoria cache. Prima che il processore possa caricare una riga, deve assicurarsi che una versione valida dei dati sia effettivamente nella memoria principale, ovvero che nessuna copia modificata della riga sia in altre cache. La sequenza di operazioni formata in questo caso si chiama legge con l'intento di modificarezioni(RWITM, Leggi con l'intento di modificare). Se viene trovata una copia della linea richiesta in una delle cache e nello stato M, il processore con questa copia interrompe la sequenza RWITM e riscrive la linea nell'OP, dopodiché cambia lo stato della linea nella sua cache a I. Quindi la sequenza RWITM viene ripresa e riacceso alla memoria principale per leggere la riga aggiornata. Lo stato finale della linea sarà M, in cui non ne esiste una copia più affidabile né nell'OP né in altre cache. Se una copia della linea esisteva in un'altra cache e non aveva uno stato M, tale copia viene scartata e l'accesso alla memoria principale viene eseguito immediatamente.

Una cache di lettura non modifica lo stato della riga in lettura. Se il processore esegue l'accesso in scrittura a una linea esistente nello stato S, trasmette al bus per informare le altre cache, aggiorna la linea nella sua cache e la imposta sullo stato M. Tutte le altre copie della linea vengono spostate nello stato I. Se il processore effettua l'accesso in scrittura alla linea nello stato E, l'unica cosa che deve fare è scrivere sulla linea e cambiare il suo stato in M, poiché non ci sono altre copie della linea nel sistema.

Nella fig. 11.15 mostra una tipica sequenza di eventi in un sistema di due processori che richiedono l'accesso alla cella x. L'accesso a qualsiasi cella in una riga della cache è considerato un accesso all'intera riga.

Illustriamo le fasi in cui il processore 2 tenta di leggere il contenuto della cella x "(Fig. 11.16). Innanzitutto, si verifica un errore di lettura della cache e il processore tenta di accedere alla memoria principale. Il processore 1 monitora il bus, rileva l'accesso a un cella, una copia della quale è nella sua memoria cache ed è in

|

Riso. 11.16. Transizione dallo stato E allo stato S nel protocollo MESI: a- processore 2

legge x; b - il processore 1 riscrive x "nella memoria principale;

i - il processore 2 legge x "dalla memoria principale

stato M, quindi blocca l'operazione di lettura dal processore 2. Quindi il processore 1 riscrive la riga contenente x "nell'OP e libera il processore 2 in modo che possa ripetere l'accesso alla memoria principale. Ora il processore 2 riceve la riga contenente x" e lo carica nella cache. Entrambe le copie sono contrassegnate come S.

Finora è stata considerata una versione riscrivibile del protocollo MESI. Tenendo conto di una singola scrittura, il diagramma di stato mostrato in Fig. 11.14, leggermente modificata. Tutti i miss della cache di lettura causano una transizione allo stato S. Il primo hit di scrittura è seguito da una transizione allo stato E (una cosiddetta transizione write-once). Il prossimo colpo durante la scrittura comporta un cambiamento nello stato della linea in M.

Protocolli basati su directory

Protocolli di coerenza basati su directory tipico dei sistemi complessi multiprocessore con memoria condivisa, dove i processori sono uniti da una rete di interconnessione gerarchica multistadio. La complessità della topologia rende costoso e inefficiente l'uso dei protocolli di sorveglianza con il loro meccanismo di trasmissione.

I protocolli basati su directory raccolgono e tengono traccia delle informazioni sui contenuti di tutte le cache locali. Tali protocolli sono generalmente implementati con un controller centralizzato che è fisicamente parte del controller di memoria principale. Il libro di riferimento stesso è archiviato nella memoria principale. Quando il controller della cache locale effettua una richiesta, il controller della directory rileva tale richiesta e genera le istruzioni necessarie per trasferire i dati dalla memoria principale o da un'altra cache locale contenente l'ultima versione dei dati richiesti. Il controller centrale è responsabile dell'aggiornamento delle informazioni sullo stato delle cache locali, quindi deve essere informato di qualsiasi azione locale che potrebbe influenzare lo stato del blocco dati.

La directory contiene molte voci che descrivono ogni posizione di memoria memorizzata nella cache che può essere condivisa dai processori di sistema. Il riferimento viene fatto ogni volta che uno dei processori modifica una copia di tale cella nella sua memoria locale. In questo caso, sono necessarie informazioni dalla directory per invalidare o aggiornare le copie della cella modificata (o l'intera riga contenente questa cella) in altre cache locali in cui tali copie sono disponibili.

Per ogni stringa condivisa, di cui una copia può essere inserita nella memoria cache, viene allocata una voce nella directory che memorizza i puntatori a una copia di questa stringa. Inoltre, in ogni record viene evidenziato un bit di modifica (D) che indica se la copia è sporca (D = 1 - sporca) o pulita (D = 0 - pulita), ovvero se il contenuto della riga nella cache hanno cambiato memoria dopo che è stato caricato lì. Questo bit indica se il processore è autorizzato a scrivere su questa stringa.

Attualmente, esistono tre modi noti per implementare i protocolli di coerenza della cache basati su directory: il riferimento completo, il riferimento limitato e il riferimento concatenato.

Nel protocollo riferimento completo una singola directory centralizzata mantiene le informazioni su tutte le cache. Il riferimento è memorizzato nella memoria principale.

|

Riso. 11.17. Protocollo di coerenza della cache di riferimento completo

In un sistema di N processori, ogni voce di directory conterrà n puntatori a un bit. Se è presente una copia dei dati nella memoria cache locale corrispondente, il bit del puntatore viene impostato a 1, altrimenti - a 0. Il diagramma con il riferimento completo è mostrato in Fig. 11.17. Ciò presuppone che ci sia una copia della riga in ogni cache. Ad ogni riga sono assegnati due indicatori di stato: un bit valido (V, Valido) e un bit di proprietà (P, Privato). Se le informazioni nella riga sono corrette, il suo V-bit è impostato a 1. Un singolo valore del P-bit indica che il dato processore ha il diritto di scrivere sulla riga corrispondente della sua memoria cache locale.

Supponiamo che il processore 2 scriva nella posizione x. Inizialmente, il processore non ha ancora ricevuto l'autorizzazione per tale registrazione. Forma una richiesta al controller della directory e attende l'autorizzazione per continuare l'operazione. In risposta a una richiesta a tutte le cache in cui sono presenti copie della riga contenente la cella x, viene emesso un segnale per eliminare le copie esistenti. Ogni cache che riceve questo segnale reimposta il bit di validità della stringa nullable (V-bit) su 0 e restituisce un segnale di riconoscimento al controller di directory. Dopo aver ricevuto tutti i segnali di conferma, il controller di directory imposta il bit di modifica (D-bit) della voce di directory corrispondente a uno e invia un segnale al processore 2 per abilitare la scrittura nella cella x. Da questo punto in poi, il processore 2 può continuare a scrivere sulla propria copia della cella x, oltre che sulla memoria principale, se lo schema di write-through è implementato nella cache.

I problemi principali del protocollo di directory completo sono legati al gran numero di voci. Per ogni cella nel riferimento di sistema di N processori, è richiesto N + 1 bit, cioè con un aumento del numero di processori, il coefficiente di complessità aumenta linearmente. Il protocollo di directory completo consente a ciascuna cache locale di avere copie di tutte le celle condivise. In pratica, tale possibilità non rimane sempre richiesta: in un dato momento, di solito sono rilevanti solo una o più copie. V protocollocon riferimento limitato le copie di una singola riga possono trovarsi solo in un numero limitato di cache - non possono essercene più di P copie della stringa, mentre il numero di puntatori nelle voci della directory è ridotto a n (n< N ). Per identificare in modo univoco la memoria cache che memorizza la copia, il puntatore invece di un bit dovrebbe essere costituito da log2 N bit e la lunghezza totale dei puntatori in ciascuna voce di directory, invece di N bit sarà uguale Plog2n morso. Con un valore costante P il tasso di crescita del fattore di complessità di una directory ristretta all'aumentare delle dimensioni del sistema è inferiore rispetto al caso di una relazione lineare.

Quando più di P copie, il titolare decide quale delle copie conservare e quale cancellare, dopodiché vengono apportate le corrispondenti modifiche agli indici delle voci di rubrica.

Metodo directory collegate mira anche a comprimere il volume del libro di riferimento. Utilizza un elenco collegato per memorizzare i record, che possono essere implementati come uno collegato (unidirezionale) e doppiamente collegato (bidirezionale).

Riso. 11.18. Protocollo di coerenza della cache della directory concatenata

In un elenco con collegamenti singoli (Figura 11.18), ogni voce di directory contiene un puntatore a una copia della stringa in una delle cache locali. Copie di righe con lo stesso nome in diverse cache di sistema formano una catena unidirezionale. Per fare ciò, i loro tag forniscono un campo speciale in cui viene inserito un puntatore alla memoria cache contenente la copia successiva della catena. nel tag ultima copia nella catena viene inserito un carattere delimitatore speciale. Il riferimento concatenato consente stringhe di lunghezza N, cioè, supporta n copie della cellula. Quando si crea un'altra copia, la catena deve essere distrutta e al suo posto deve essere formata una nuova. Supponiamo, ad esempio, che il processore 5 non abbia una copia della cella x e si rivolga alla memoria principale per essa. Il puntatore nella directory viene modificato in modo da puntare alla cache numero 5 e il puntatore nella cache 5 - in modo tale da puntare alla cache 2. Per questo, il controller di memoria principale, insieme ai dati richiesti, deve trasferire anche il puntatore alla cache alla memoria cache 5 - memoria con il numero 2. Solo dopo che l'intera struttura della catena è stata formata, il processore 5 riceverà il permesso di accedere alla cella x. Se il processore scrive su una cella, viene inviato un segnale di invalidazione lungo il percorso definito dalla corrispondente catena di puntatori. La catena deve essere aggiornata quando una copia viene eliminata da qualsiasi memoria cache.

Un elenco doppiamente collegato supporta sia i puntatori avanti che indietro. Ciò consente di inserire in modo più efficiente nuovi puntatori nella catena o di eliminare da essa non più necessari, ma richiede la memorizzazione di un numero maggiore di puntatori.

Gli schemi basati su directory soffrono di congestione nel controller centralizzato, nonché sovraccarico di comunicazione nei percorsi tra i controller della cache locale e il controller centrale. Tuttavia, risultano essere molto efficaci in sistemi multiprocessore con complessa topologia di interconnessione tra processori, dove non è possibile implementare protocolli di monitoraggio.

Di seguito è riportata una breve descrizione dei protocolli attualmente rilevanti per garantire la coerenza della memoria cache basata sul libro di riferimento. Per una conoscenza dettagliata di questi protocolli, sono forniti i collegamenti alle corrispondenti fonti letterarie.

ProtocolloCodolo. Esiste una directory globale centralizzata che contiene una copia completa di tutte le informazioni sulla directory per ciascuna delle cache locali. Questo porta al problema colli di bottiglia e richiede anche la ricerca delle voci corrispondenti.

Protocolloincensiere. Lo schema di riferimento Censier utilizza un vettore di bit puntatore per indicare quali processori contengono una copia locale di un determinato blocco di memoria. Esiste un tale vettore per ogni blocco di memoria. Gli svantaggi di questo metodo sono la sua inefficacia in un largo numero processori e richiede anche l'accesso alla memoria principale per aggiornare le linee della cache.

ProtocolloArchibaldo. Lo schema di riferimento di Archibald è una coppia di schemi complessi per reti di processori organizzate gerarchicamente. CON descrizione dettagliata questo protocollo può essere trovato in.

ProtocolloStenstrom. Il manuale Stenstrom fornisce sei stati validi per ogni blocco di dati. Questo protocollo è relativamente semplice e adatto a qualsiasi topologia di interconnessione del processore. Il riferimento è memorizzato nella memoria principale. In caso di mancata lettura della cache, si accede alla memoria principale, che invia un messaggio alla cache proprietaria del blocco, se presente. Alla ricezione di questo messaggio, il proprietario della cache invia i dati richiesti e inoltra anche un messaggio a tutti gli altri processori che condividono questi dati per consentire loro di aggiornare i propri vettori di bit. Lo schema non è molto efficiente con un gran numero di processori, tuttavia è attualmente il protocollo basato su directory più maturo e ampiamente utilizzato.

Controllo domande

1. Analizzare l'influenza delle caratteristiche di AC con memoria condivisa e AC con memoria distribuita sullo sviluppo del software. Perché questi VS sono chiamati, rispettivamente, fortemente accoppiati e debolmente accoppiati?

2. Spiegare l'idea di indirizzi di memoria alternati. Quali sono le considerazioni per la scelta di un meccanismo di allocazione degli indirizzi? In che modo è correlato alla classe di architettura BC?

3. Fornire una descrizione comparativa di approcci omogenei ed eterogenei

alla memoria.

4. Quali sono i vantaggi dell'architettura SOMA?

5. Spendi analisi comparativa modelli con accesso cache-coherent e cache-incoerente alla memoria eterogenea.

6. Formulare i vantaggi e gli svantaggi dell'architettura senza accesso diretto alla memoria remota.

7. Spiegare il significato di memoria distribuita e condivisa.

8. Sviluppa il tuo esempio per illustrare il problema di coerenza della cache.

9. Descrivere le caratteristiche delle soluzioni software al problema della coerenza, evidenziarne vantaggi e debolezze.

10. Confronta le tecniche write-to-write con quelle write-off e write-to-broadcast, mettendo in evidenza i loro meriti e demeriti.

11. Fornire una descrizione comparativa dei metodi per mantenere la coerenza nei sistemi multiprocessore.

12. Esegui un'analisi comparativa dei protocolli di osservazione che conosci.

13. Quale dei protocolli di osservazione è il più popolare? Giustifica le ragioni del maggiore interesse per lui.

14. Fornire una descrizione dettagliata dei protocolli di coerenza basati sul libro di riferimento e sui metodi della loro attuazione. Quali sono le differenze tra questi protocolli e i protocolli di osservazione?

Classificazione dei sistemi MKMD

In un sistema MCMD, ogni elemento di elaborazione (PE) esegue il suo programma in modo del tutto indipendente dagli altri PE. Allo stesso tempo, gli elementi di elaborazione devono in qualche modo interagire tra loro. La differenza nel modo di tale interazione determina la divisione condizionale dei sistemi MCMD in AC con memoria condivisa e sistemi con memoria distribuita (Fig. 5.7).

Nei sistemi a memoria condivisa, caratterizzati come strettamente accoppiati, esiste una memoria condivisa di dati e istruzioni a disposizione di tutti gli elementi di elaborazione utilizzando un bus comune o una rete di connessioni. Tali sistemi sono chiamati multiprocessori. Fanno parte di questa tipologia i multiprocessori simmetrici (UMA (SMP), Symmetric Multiprocessor), i sistemi con accesso alla memoria non uniforme (NUMA, Non-Uniform Memory Access) e i sistemi con la cosiddetta memoria locale anziché la memoria cache (COMA, Cache Only Memory Access ).

Se tutti i processori hanno uguale accesso a tutti i moduli di memoria e a tutti i dispositivi I/O e ciascun processore è intercambiabile con altri processori, tale sistema viene chiamato sistema SMP. Nei sistemi con memoria condivisa, tutti i processori hanno pari opportunità di accedere a un singolo spazio di indirizzi. Una singola memoria può essere costruita come un blocco singolo o modulare, ma di solito è il caso.

I sistemi SMP appartengono all'architettura UMA. Sistemi informatici La memoria condivisa, in cui qualsiasi processore accede alla memoria in modo uniforme e impiega la stessa quantità di tempo, è chiamata sistemi UMA (Uniform Memory Access).

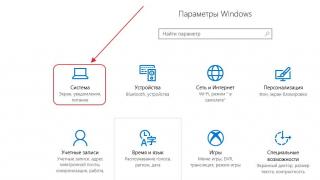

Dal punto di vista dei livelli di memoria utilizzata nell'architettura UMA, vengono considerate tre opzioni per costruire un multiprocessore:

Classic (solo con memoria principale condivisa);

Con cache locale aggiuntiva per ogni processore;

Con memoria buffer locale aggiuntiva per ogni processore (Figura 5.8).

Dal punto di vista del modo in cui i processori interagiscono con le risorse condivise (memoria e CBV), nel caso generale si distinguono le seguenti tipologie di architetture UMA:

Con bus comune e divisione temporale (7.9);

Con un interruttore a barra trasversale;

Basato su reti multistadio.

L'utilizzo di un solo bus limita la dimensione di un multiprocessore UMA a 16 o 32 processori. Per ottenere una taglia più grande è necessario un tipo diverso rete di comunicazione... Lo schema di connessione più semplice è un interruttore a barra trasversale (Figura 5.10). Gli interruttori a barra incrociata sono stati utilizzati per decenni per collegare casualmente un gruppo di linee in entrata a un numero di linee in uscita.

La traversa è una rete non bloccante. Ciò significa che il processore sarà sempre associato al blocco di memoria corretto, anche se qualche linea o nodo è già occupato. Inoltre, non è richiesta alcuna pianificazione preliminare.

Gli interruttori a barra incrociata sono abbastanza adatti per sistemi di medie dimensioni (Figura 5.11).

Basato su switch 2x2, puoi costruire reti multistadio. Una possibile opzione è la rete omega (Figura 5.12). Per n processori e n moduli di memoria, sono necessari log 2 n passaggi, n / 2 interruttori per ogni passaggio, ovvero un totale di (n / 2) log 2 n passaggi per ogni passaggio. Questo è molto meglio di n 2 nodi (punti di intersezione), specialmente per grandi n.

I multiprocessori UMA a bus singolo sono generalmente limitati a diverse decine di processori, mentre i multiprocessori coordinati o i multiprocessori con switch richiedono un costoso Hardware e non sono molto più grandi. Per ottenere più di 100 processori, è necessario un diverso accesso alla memoria.

Per una maggiore scalabilità dei multiprocessori, viene adattata l'architettura con accesso alla memoria non uniforme NUMA (NonUniform Memory Access). Come i multiprocessori UMA, forniscono un unico spazio di indirizzi per tutti i processori, ma a differenza delle macchine UMA, l'accesso ai moduli di memoria locale è più rapido rispetto ai moduli di memoria remoti.

Nell'ambito del concetto NUMA, vengono implementati gli approcci indicati con le abbreviazioni NC-NUMA e CC-NUMA.

Se il tempo di accesso alla memoria remota non è nascosto (perché non c'è memoria cache), tale sistema è chiamato NC-NUMA (No Caching NUMA - NUMA senza cache) (Fig.5.13).

Se sono presenti cache coerenti, il sistema è denominato CC-NUMA (Coherent Cache Non-Uniform Memory Architecture - NUMA with consistent cache) (7.14).

Memoria principale

Memoria principale è un dispositivo di archiviazione direttamente connesso al processore e progettato per memorizzare programmi eseguibili e dati direttamente coinvolti nelle operazioni. Ha prestazioni sufficienti, ma volume limitato. La memoria principale è suddivisa in vari tipi, i principali dei quali sono la memoria ad accesso casuale (RAM) e la memoria di sola lettura (ROM) (Fig. 1).

La RAM è progettata per memorizzare le informazioni (programmi e dati) direttamente coinvolte in processo di calcolo nell'attuale fase di funzionamento.

La RAM viene utilizzata per ricevere, archiviare ed emettere informazioni. È in esso che il processore "prende" programmi e dati iniziali per l'elaborazione, in cui scrive i risultati. Questa memoria ha preso il nome di "operativa" perché funziona molto velocemente, quindi il processore praticamente non deve aspettare durante la lettura dei dati dalla memoria e la scrittura nella memoria. Tuttavia, i dati in esso contenuti vengono conservati solo quando il computer è acceso. Quando si spegne il computer, il contenuto della RAM viene cancellato. Pertanto, la RAM è memoria volatile.

Riso. 1. I principali tipi di memoria principale

Spesso la designazione RAM (memoria ad accesso casuale, cioè memoria con accesso casuale). L'accesso casuale è inteso come la capacità di accedere direttamente a qualsiasi cella di memoria specificata (arbitraria) e il tempo di accesso per qualsiasi cella è lo stesso.

La RAM è basata su grandi circuiti integrati contenenti matrici di elementi di immagazzinamento a semiconduttore (trigger). Gli elementi di immagazzinamento si trovano all'intersezione dei bus verticale e orizzontale della matrice; la registrazione e la lettura delle informazioni viene effettuata applicando impulsi elettrici attraverso quei canali della matrice, che sono collegati agli elementi appartenenti alla cella di memoria selezionata.

La quantità di RAM installata nel computer influisce non solo sulla capacità di lavorare con programmi ad alta intensità di risorse, ma anche sulle sue prestazioni, poiché quando non c'è abbastanza memoria, viene utilizzato un disco rigido come estensione logica, il cui tempo di accesso è incomparabilmente più lungo. Oltre alla quantità di RAM, le prestazioni di un computer sono influenzate anche dalla sua velocità e dal metodo utilizzato per scambiare dati tra il microprocessore e la memoria.

L'OP è implementato su chip DRAM (OP dinamico), che, rispetto ad altri tipi di memoria, sono caratterizzati da basso costo e alta capacità specifica, ma elevato consumo energetico e prestazioni inferiori. Ciascun byte di dati (0 e 1) nella DRAM viene memorizzato come carica del condensatore. A causa della presenza di correnti di dispersione, la carica del condensatore deve essere rinnovata ad intervalli regolari. A causa della continua necessità di aggiornamento, tale memoria è chiamata memoria dinamica. La rigenerazione del contenuto della memoria richiede tempo aggiuntivo e la registrazione delle informazioni nella memoria durante la rigenerazione non è consentita.

Il costo della RAM è recentemente diminuito drasticamente (dall'estate del 1995 all'estate del 1996 - più di 4 volte), quindi le grandi richieste di molti programmi e sistemi operativi per la RAM da un punto di vista finanziario sono diventate meno onerose.

Per accelerare l'accesso alla RAM su computer ad alta velocità, viene utilizzata una memoria cache stabile ad altissima velocità, che si trova, per così dire, "tra" il microprocessore e la RAM e memorizza copie delle sezioni utilizzate più frequentemente di RAM. Quando il microprocessore accede alla memoria, cerca prima i dati richiesti dalla memoria cache. Poiché il tempo di accesso alla memoria cache è parecchie volte inferiore rispetto alla memoria ordinaria, e nella maggior parte dei casi i dati richiesti dal microprocessore sono già memorizzati nella memoria cache, il tempo medio di accesso alla memoria diminuisce. La memoria cache è implementata su un chip SRAM (RAM statica).

Per i computer basati su Intel-386DX o 80386SX, la dimensione della cache di 64 KB è sufficiente e 128 KB sono sufficienti. I computer basati su Intel-80486DX, DX2, DX4 e Pentium dispongono in genere di 256 KB di cache.

I microprocessori della serie 486 e Pentium contengono una piccola memoria cache interna, quindi, per terminologia univoca, a volte nella letteratura tecnica, la memoria cache situata sulla scheda madre è chiamata memoria cache di secondo livello.

Nel microprocessore Pentium Pro, la memoria cache L2 è contenuta in un unico pacchetto con il processore stesso (si può dire che è integrata nel microprocessore).

Non è necessario avere tutta la memoria, le informazioni in cui devono cambiare. È meglio conservare alcune delle informazioni più importanti in modo permanente nella memoria del computer. Questa memoria è chiamata persistente. I dati sono stati inseriti nella memoria permanente durante la sua fabbricazione. Di norma, questi dati non possono essere modificati, i programmi in esecuzione sul computer possono solo leggerli. Questo tipo di memoria è solitamente chiamato ROM (memoria di sola lettura) o ROM (memoria di sola lettura).

Sul PC IBM - computer compatibile la memoria permanente memorizza programmi per testare apparecchiature, un computer, avviare il caricamento del sistema operativo (OS) ed eseguire funzioni di base per la manutenzione dei dispositivi del computer. Poiché la maggior parte di questi programmi sono relativi al servizio I/O, i contenuti della memoria di sola lettura sono spesso chiamati BIOS (Basic Input - Output System).

Molti computer installano un BIOS basato sulla memoria FLASH. Questa memoria può essere modificata dai programmi, che consente di aggiornare il BIOS utilizzando programmi speciali, senza sostituire la scheda madre o il chip del BIOS.

Tutti i computer, tranne quelli molto vecchi, contengono anche un programma di configurazione del computer (SETUP) nel BIOS. Consente di impostare alcune caratteristiche dei dispositivi informatici (tipi di controller video, dischi fissi e unità floppy, alcune anche modalità di funzionamento con RAM, richiesta di password all'avvio, ecc.). Tipicamente, il programma di configurazione viene invocato se l'utente, durante bootstrap premerà una chiave specifica o una combinazione di tasti (il più delle volte il tasto Canc).

Capacità di memoria FLASH da 32 Kbyte a 2 Mbyte, tempo di accesso in lettura 0,06 μs, tempo di scrittura di un byte circa 10 μs; Memoria FLASH - memoria non volatile.

Oltre alla normale memoria ad accesso casuale e alla memoria di sola lettura, un computer ha una piccola sezione di memoria per memorizzare i parametri di configurazione del computer. Viene spesso definita memoria CMOS perché questa memoria è solitamente realizzata con tecnologia CMOS (semiconduttore di ossido di metallo complementare) a basso consumo energetico. Il contenuto della memoria CMOS non cambia allo spegnimento del computer, poiché per alimentarlo viene utilizzata una batteria speciale.

Pertanto, la capacità della memoria principale è costituita da milioni di singole celle di memoria con una capacità di 1 byte ciascuna. La capacità totale della memoria principale dei PC moderni varia solitamente da 1 a 4 GB. La capacità della RAM è di due ordini di grandezza superiore alla capacità della ROM: la ROM occupa fino a 2 MB sulle nuove schede madri), il resto è RAM.

ORGANIZZAZIONE DELLA MEMORIA NELLE MACCHINE INFORMATICHE

Scopo, parametri di base e

Classificazione dei tipi di memoria

I dispositivi di memoria (dispositivi di archiviazione) VM sono progettati per registrare, archiviare e leggere le informazioni presentate in modulo digitale/ 2,3 /. I dispositivi di memoria, come i processori, funzionano con due tipi di informazioni: programmi e dati, quindi le caratteristiche della memoria determinano in gran parte le prestazioni e funzionalità VM.

I dispositivi di memoria funzionano in due modalità: accessi alla memoria e Deposito... Nella modalità di accesso alla memoria, le informazioni vengono registrate o le informazioni vengono lette dalla memoria. Se non si accede alla memoria, entra in modalità di archiviazione.

I principali parametri che caratterizzano i dispositivi di memoria sono la capacità di informazione (volume), le prestazioni, il consumo energetico e il costo / 2,5,8 /.

Capacità di informazione (volume) il dispositivo di memoria è definito numero massimo informazioni memorizzate e viene misurato in byte, KByte, MByte, GByte e TByte.

1 KB = 2 10 byte; 1MB = 2 20 byte; 1 GB = 2 30 byte e 1 TB = 2 40 byte.

Le prestazioni della memoria sono caratterizzate dai seguenti parametri principali:

tempo di campionamento (accesso) t B, determinato dall'intervallo di tempo tra i momenti del segnale di campionamento (l'inizio del ciclo di lettura) e la ricezione dei dati letti all'uscita della memoria;

durata del ciclo t Ц, che è determinato dall'intervallo di tempo minimo consentito tra successivi accessi alla memoria. Considerando che l'accesso alla memoria significa scrivere o leggere, a volte si separano la durata del ciclo di lettura t C.RT... e la durata del ciclo di registrazione t Ts.ZP. per tipi di memoria in cui questi tempi di ciclo sono diversi, es. t CH. t C.ZP .

Nel caso generale, il ciclo di accesso è costituito da una fase di fetch (accesso) e da una fase di rigenerazione (recupero) della memoria, quindi t C> t V.

Le prestazioni della memoria possono essere caratterizzate anche dalla velocità di trasferimento dei dati scritti o letti e misurata in MB/s.

Il consumo di energia per molti tipi di memoria in modalità di accesso è significativamente maggiore rispetto alla modalità di archiviazione. La memoria non volatile in modalità di archiviazione non consuma energia. Ma un certo numero di tipi di memoria, ad esempio la memoria dinamica elettronica, richiedono cicli di rigenerazione in modalità di archiviazione, quindi il consumo di energia in questa modalità è paragonabile al consumo di energia in modalità di accesso.

Per confronto tipi diversi memoria, è conveniente utilizzare un consumo energetico ridotto a una cella (cioè specifico) e il costo dei dispositivi di memoria.

Un importante parametro di memoria è anche larghezza del bus dati di memoria, definire il numero di byte con cui è possibile eseguire contemporaneamente un'operazione di lettura o scrittura.

I dispositivi di memoria VM possono essere classificati secondo vari criteri: dal principio fisico di funzionamento, dallo scopo funzionale, dal modo di organizzazione, dalla necessità di alimentazione in modalità di archiviazione, ecc.

Secondo il principio fisico di funzionamento, la memoria è classificata in elettronica, magnetica, ottica, magnetica - ottica.

Memoria elettronica eseguita su elementi semiconduttori e implementata sotto forma di LSI. La memoria elettronica è suddivisa in statico e dinamico.

Nell'LSI della memoria statica, i trigger statici su bipolari o transistor ad effetto di campo... Come sai, il numero di stati di trigger stabili è due, il che rende possibile utilizzarlo per memorizzare un'unità di informazioni - un po'. Le celle di memoria per la memorizzazione di byte e parole utilizzano rispettivamente 8 e 16 trigger.

Nella memoria dinamica LSI, i condensatori elettrici sono usati come celle di memoria elementari. La presenza di un addebito corrisponde alla memorizzazione di un "1" logico, l'assenza di addebito corrisponde alla memorizzazione di uno "0" logico. Come condensatori di immagazzinamento vengono utilizzate le capacità interelettrodi dei transistor MOS o i condensatori creati appositamente nel cristallo LSI. Un frammento dello schema a blocchi della memoria dinamica, contenente due celle 1 e 2, è mostrato in Fig. 6.1.

Ciascuna cella di memoria elementare contiene un condensatore MOS di memoria C (decimi di pF) e un interruttore a transistor T, che collega tale condensatore al bus dati. La porta dell'interruttore MOS a transistor è collegata alla corrispondente uscita del decodificatore di indirizzo. Quando la cella è selezionata, il tasto T si apre e collega il condensatore C al bus dati. Inoltre, a seconda del tipo di comando: scrittura (WR) o lettura (RD) - tramite l'amplificatore corrispondente vengono scritti i dati di ingresso (DI) o letti i dati di uscita (DO).

Rispetto alla memoria statica, la memoria dinamica è molto più semplice, più economica e offre un grado di integrazione molto elevato, ad es. capacità specifica superiore. Ma rispetto alla memoria dinamica statica, è più lenta e richiede una rigenerazione periodica (ripristino) delle informazioni nelle celle elementari. In altre parole, è necessario ripristinare periodicamente la carica sui condensatori di accumulo C, che nel tempo si autoscaricano, cioè "Perdere" informazioni. Per fare ciò, ogni pochi millisecondi (msec) leggono le informazioni dalle celle di memoria e quindi riscrivono le informazioni, il che consente di ripristinare la carica sui condensatori di archiviazione C. La necessità di organizzare cicli di aggiornamento periodici complica alquanto la gestione della memoria dinamica.

Per i tipici moduli di memoria elettronica, il tempo di campionamento t Bè unità - decine di nanosecondi ( nsec), e la capacità di informazione è di decine - centinaia di Mbyte.

La memoria elettronica statica e dinamica è volatile, cioè. quando viene tolta l'alimentazione, le informazioni nelle celle non vengono salvate. C'è anche non volatile memoria elettronica - memoria di sola lettura (ROM), informazioni da cui durante il funzionamento della VM possono essere solo lette. Le posizioni della memoria ROM verranno discusse di seguito.

Memoria magnetica in base alla presenza di un certo numero di materiali magnetici (ad esempio ossido di ferro) due stati stabili di magnetizzazione residua di segno opposto. Tale materiali magnetici caratterizzato da un ciclo di isteresi rettangolare B = f (H), e da essi viene applicato uno strato magnetico funzionante, applicato alla superficie di vari supporti mobili: dischi magnetici. Per scrivere e leggere informazioni, vengono utilizzate testine magnetiche, che sono induttori in miniatura avvolti su un nucleo magnetico con uno spazio vuoto. Durante la registrazione, la testina magnetica magnetizza la porzione dello strato magnetico che passa sotto il gap di lavoro nella direzione determinata dalla direzione della corrente che scorre. Durante la lettura, le aree superficiali magnetizzate passano vicino alla testina di lettura induttiva e inducono impulsi emf in essa. I dispositivi di memoria che utilizzano questo principio hanno un costo specifico di memorizzazione delle informazioni molto basso, non sono volatili ma, essendo elettromeccanici, sono significativamente inferiori alle memorie elettroniche in termini di velocità, affidabilità e consumo energetico. Per le unità disco rigido, la velocità di trasferimento dei dati raggiunge le decine di MB / se la capacità delle informazioni è di centinaia di GB.

V memoria ottica per memorizzare le informazioni, viene utilizzata una modifica delle proprietà ottiche (principalmente, il grado di riflessione) della superficie del supporto. Il supporto ottico ha la forma di un disco ( Compact disk- CD), il cui strato riflettente (metal sputtering) è ricoperto da uno strato di colorante organico. Durante la registrazione, il raggio laser è modulato da un flusso di bit registrati e brucia le fosse nello strato di colorante in determinati punti della traccia. A causa della differenza del coefficiente di riflessione delle fosse e delle aree incombuste della superficie durante la lettura, si verifica una modulazione della luminosità del raggio riflesso, che codifica le informazioni lette dal CD. prodotto tipi diversi dischi CD ottici: CD-ROM (Read Only Memory) - che consente solo la lettura di informazioni scritte in modo matrice, CD-R (Recordable) - che consente almeno una scrittura su un disco e una lettura multipla, CD-RW (ReWritable) - consentendo la riscrittura multipla su disco (e ovviamente la lettura). I dischi ottici sono economici e hanno una capacità di informazione significativa (fino a un GB), sono non volatili e facilmente sostituibili, ma in termini di velocità, affidabilità e consumo energetico, come i dischi magnetici, sono significativamente inferiori alla memoria elettronica.

In termini di funzionalità, i dispositivi di memoria possono essere classificati in memoria ad accesso casuale (SRAM), memoria ad accesso casuale (RAM), memoria di sola lettura (ROM) e dispositivi di archiviazione esterni (VCD).

RAM destinato alla memorizzazione di programmi (sistema, applicazione) e dati utilizzati direttamente dalla CPU in quel momento. I tempi del ciclo di lettura e scrittura per la RAM sono generalmente gli stessi. Di solito, come RAM viene utilizzata una memoria dinamica con un volume fino a unità di GB, a seconda dello scopo e dell'ambito dell'MS.

Pozu o Memoria cache- si tratta di una piccola quantità di memoria ad alta velocità, in cui la durata del ciclo di accesso t C è inferiore alla durata del ciclo macchina del processore. Pertanto, quando si accede alla memoria cache, non è necessario introdurre cicli di attesa del processore nei cicli di accesso alla memoria della macchina. La memoria cache è una memoria buffer tra RAM e CPU ed è basata sulla memoria statica. La cache memorizza copie di blocchi (pagine) di programmi e dati di quelle aree della RAM a cui è stato effettuato l'ultimo accesso, nonché una directory, un elenco della loro corrispondenza attuale con le aree della RAM. Ad ogni accesso alla memoria principale, il controller della cache della directory verifica se nella cache è presente una copia valida del blocco (pagina) richiesto. Se c'è una copia, allora questo è il caso. hit della cache e solo la memoria cache è accessibile per dati o codice. Se non c'è una copia valida, allora questo è il caso. perdere soldi, e il blocco richiesto (pagina) dalla RAM viene scritto nella cache e la scrittura viene eseguita nella posizione del blocco (pagina) meno effettivo precedentemente eliminato dalla cache nella RAM, ad es. il blocco di informazioni, il numero di chiamate a cui è stato il più piccolo. A causa dei programmi e dei dati inerenti tali proprietà fondamentali, come spaziale e località temporanea/ 2,7,13 / il numero di cache hit è molte volte maggiore del numero di cache miss anche con dimensioni di memoria cache ridotte (unità - decine di KB). Pertanto, l'utilizzo della memoria cache migliora notevolmente le prestazioni della VM. Solitamente, la cache è implementata secondo uno schema a tre livelli: la cache primaria (L1 Cache), di decine di KB, e la cache secondaria (L2 Cache), centinaia di KB, situata nel cristallo MP, il terzo livello cache (L3 Cache), le unità di MB sono installate sulla scheda madre o nell'edificio MP.

romÈ una memoria elettronica non volatile che viene utilizzata per memorizzare informazioni invariate o raramente modificate durante il funzionamento di una VM: software di sistema (BIOS), software applicativo per VM embedded e on-board, set di tabelle, parametri di configurazione di vari sistemi, ecc. La principale modalità di funzionamento della ROM è la lettura, che dà origine a un altro nome comune per tale memoria ROM (Read Only Memory). La scrittura di informazioni su ROM, chiamata programmazione, è solitamente molto più difficile, richiede più tempo ed energia rispetto alla lettura.

VCU progettato per l'archiviazione non volatile di grandi volumi in un certo modo informazioni strutturate: archivi, banche dati, archivi. Caratteristica memoria esterna è che i suoi dispositivi funzionano con blocchi di informazioni e non byte o parole, come consente la RAM. Inoltre, il processore può accedere all'OVC solo tramite la RAM. Le unità disco (HDD, CD) vengono solitamente utilizzate come VCU, che possono memorizzare centinaia di GB di informazioni.

Memoria elettronica tampone incluso nei controller di vari dispositivi esterni, risolvere problemi visualizzazione e immissione di informazioni, attività di comunicazione, conversione del segnale, ecc. La presenza della memoria buffer consente di coordinare velocità di trasferimento dati notevolmente diverse del bus di sistema e dei dispositivi esterni, ridurre il tempo trascorso da ciascuno dei dispositivi esterni sul bus di sistema e aumentare le prestazioni della VM.

Il modo di organizzare la memoria è determinato dal metodo di collocazione e ricerca delle informazioni nella memoria. Su questa base, distinguere tra indirizzo, organizzazione della memoria associativa e stack.

V memoria indirizzi per accedere alle celle di memoria, vengono utilizzate indirizzi, che sono intesi come codici di numeri di celle di memoria. L'organizzazione indirizzabile della memoria consente di accedere alle celle di memoria tramite i loro indirizzi in un ordine arbitrario e la durata del ciclo di accesso è la stessa per tutte le celle, indipendentemente dall'indirizzo. Pertanto, per denominare tale memoria viene utilizzato anche il termine "memoria ad accesso casuale (RAM)" o RAM (memoria ad accesso casuale). Ad esempio, RAM e ROM hanno un'organizzazione di memoria indirizzabile.

V memoria associativa(ADS) le informazioni vengono ricercate non dagli indirizzi delle celle di memoria, ma dal loro contenuto o parte di esso. Nel caso generale, una richiesta alla memoria associativa viene effettuata specificando una lista di bit in base alla quale ricercare una cella di memoria, e specificando il contenuto dei bit allocati. L'elenco delle cifre per la ricerca è impostato in registro-maschera. Questo registro ha la stessa larghezza di bit della cella di memoria CAM e ne contiene solo in quei bit che si stanno cercando. V caso-contesto il contenuto di questi bit è impostato e la sua larghezza di bit è uguale alla larghezza di bit del registro maschera.

Se viene trovata una cella con una data combinazione di zero e uno, il CAM genera una risposta positiva indicando l'indirizzo della cella trovata. Successivamente, l'indirizzo viene trasmesso al decodificatore di indirizzi e l'intero contenuto di tale cella può essere letto o è possibile scrivervi nuovi contenuti. In caso contrario, l'AMS genera una risposta negativa alla richiesta.

La ricerca delle informazioni per contesto nella CAM viene effettuata contemporaneamente in tutte le celle di memoria, quindi la CAM è molte volte più veloce della RAM, ma è anche molto più costosa. Nei moderni sistemi informatici, le CAM vengono utilizzate, ad esempio, come parte della memoria cache.

Stack di memoria(Stack), oltre che associativo, non è indirizzato. Uno stack può essere visto come un insieme di celle che formano una matrice unidimensionale, in cui le celle adiacenti sono collegate tra loro da catene di trasmissione di parole di bit. In questa memoria, la scrittura e la lettura vengono eseguite secondo la regola "l'ultimo scritto viene letto per primo" o "Last Input First Output (LIFO)". Pertanto, lo stack è chiamato memoria "push" con ordine inverso leggere ad alta voce. Di solito lo stack è organizzato in RAM. Il numero di parole nello stack è determinato dal puntatore dello stack SP e la scrittura e la lettura dallo stack vengono eseguite rispettivamente dai comandi PUSH e POP. La memoria stack è ampiamente utilizzata, come già discusso in precedenza, durante la gestione degli interrupt e la chiamata di subroutine.

Insieme alla memoria stack, si è diffusa la memoria acquistata in negozio con ordine di lettura diretto, ad es. "La prima scritta viene letta per prima" o "Primo ingresso prima uscita (FIFO)". Questa memoria è chiamata memoria buffer e, come lo stack, è organizzata in RAM.

Organizzazione del sottosistema di memoria in un PC

Le memorie del sottosistema di memoria del PC possono essere organizzate nella seguente gerarchia (Tabella 9.1):

| Tabella 9.1. La gerarchia del sottosistema di memoria del PC | ||||||||

| № | Tipo di memoria | 1985 anno | 2000 anni | |||||

| Tempo di campionamento | Volume tipico | Prezzo / Byte | Tempo di campionamento | Volume tipico | Prezzo / Byte | |||

| Memoria superoperativa (registri) | 0,2 5 ns | 16/32 bit | $ 3 - 100 | 0,01 1 ns | 32/64/128 bit | $ 0,1 10 | ||

| Archiviazione buffer ad alta velocità (cache) | 20 100 ns | 8Kb - 64Kb | ~ $ 10 | 0,5 - 2 ns | 32 Kb 1 Mb | $ 0,1 - 0,5 | ||

| Memoria operativa (principale) | ~ 0,5 ms | 1MB - 256MB | $ 0,02 1 | 2 ns 20 ns | 128 MB - 4 GB | $ 0,01 0,1 | ||

| Memoria esterna (memoria di massa) | 10 - 100 ms | 1MB - 1GB | $ 0,002 - 0,04 | 5 - 20 ms | 1 GB - 0,5 TB | $ 0,001 - 0,01 |

I registri del processore costituiscono il suo contesto e memorizzano i dati utilizzati dalle istruzioni del processore attualmente in esecuzione. I registri del processore sono generalmente accessibili tramite le loro designazioni mnemoniche nelle istruzioni del processore.

La cache viene utilizzata per abbinare la velocità della CPU e della memoria principale. I sistemi informatici utilizzano una cache multilivello: cache di livello I (L1), cache di livello II (L2), ecc. I sistemi desktop in genere utilizzano una cache a due livelli, mentre i sistemi server utilizzano una cache a tre livelli. La cache memorizza istruzioni o dati che potrebbero essere inviati al processore per l'elaborazione nel prossimo futuro. Il funzionamento della cache è trasparente al software, quindi la cache di solito non è accessibile dal software.

Memoria RAM, di regola, funzionalmente completa moduli software(il kernel del sistema operativo, i programmi eseguibili e le loro librerie, i driver di dispositivo, ecc.) e i loro dati, direttamente coinvolti nel funzionamento dei programmi, ed è anche utilizzato per salvare i risultati di calcoli o altre elaborazioni di dati prima di inviarli a un memoria, a un'uscita dati del dispositivo o alle interfacce di comunicazione.

Ad ogni cella di memoria è assegnato un indirizzo univoco. I metodi di allocazione della memoria organizzativa forniscono ai programmatori la capacità di uso efficace l'intero sistema informatico. Questi metodi includono il modello di memoria continua ("flat") e il modello di memoria segmentata. Quando si utilizza un modello di memoria piatto, il programma opera con un singolo spazio di indirizzi contiguo, uno spazio di indirizzi lineare, in cui le celle di memoria sono numerate in modo sequenziale e continuo da 0 a 2n-1, dove n è la capacità della CPU all'indirizzo. Quando si utilizza un modello segmentato per un programma, la memoria è rappresentata da un gruppo di blocchi di indirizzi indipendenti chiamati segmenti. Per indirizzare un byte di memoria, un programma deve utilizzare un indirizzo logico costituito da un selettore di segmento e un offset. Il selettore di segmento seleziona un segmento specifico e l'offset punta a una cella specifica nello spazio degli indirizzi del segmento selezionato.

I metodi organizzativi di allocazione della memoria consentono di organizzare un sistema informatico in cui lo spazio degli indirizzi di lavoro del programma supera la dimensione della RAM effettivamente disponibile nel sistema, mentre la mancanza di RAM è riempita da memoria esterna più lenta o più economica (disco rigido , memoria flash, ecc.) ) Questo concetto è chiamato memoria virtuale. In questo caso, lo spazio degli indirizzi lineare può essere mappato allo spazio degli indirizzi fisico direttamente (un indirizzo lineare è un indirizzo fisico) o utilizzando il meccanismo di paging. Nel secondo caso, lo spazio di indirizzamento lineare è suddiviso in pagine di uguale dimensione che costituiscono la memoria virtuale. Il paging fornisce una mappatura delle pagine di memoria virtuale richieste allo spazio di indirizzi fisico.

Oltre all'implementazione del sistema di memoria virtuale, vengono utilizzati dispositivi di archiviazione esterni per conservazione a lungo termine programmi e dati sotto forma di file.

Memoria cache

La memoria cache è un dispositivo di archiviazione ad alta velocità situato sullo stesso die della CPU o esterno alla CPU. La cache funge da buffer ad alta velocità tra la CPU e la memoria principale relativamente lenta. L'idea della memoria cache si basa sulla previsione degli accessi più probabili della CPU alla RAM. Questo approccio si basa sul principio della località temporale e spaziale del programma.

Se la CPU ha avuto accesso a un oggetto nella RAM, è molto probabile che presto farà nuovamente riferimento a quell'oggetto. Un esempio di questa situazione potrebbe essere il codice oi dati nei cicli. Questo concetto è descritto dal principio della località temporanea, secondo il quale gli oggetti della memoria principale di uso frequente dovrebbero essere "più vicini" alla CPU (nella cache).

Vengono utilizzati tre metodi di scrittura per riconciliare il contenuto della cache e della RAM:

- Write through: contemporaneamente alla memoria cache, la RAM viene aggiornata.

- Scrittura bufferizzata: le informazioni vengono ritardate nel buffer della cache prima di essere scritte nella RAM e riscritte nella RAM in quei cicli quando la CPU non vi accede.

- Riscrittura: viene utilizzato il bit di modifica nel campo tag e la riga viene riscritta nella RAM solo se il bit di modifica è 1.